# Design and analysis of a CFCFC OTA based on the Behavioral Modeling of a $4^{th}$ Order Low-Pass Hybrid $\Sigma\Delta$ Modulator

[D. Calderón-Preciado, J. G. García-Sánchez, F. Sandoval-Ibarra, E. Ch. Becerra-Álvarez]

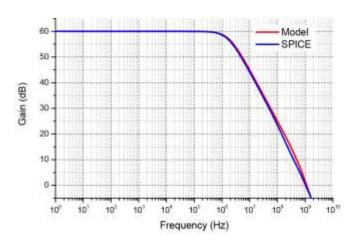

Abstract-In this paper SIMSIDES-based behavioral simulation of a 4<sup>th</sup> order Hybrid  $\Sigma \Delta$  (H $\Sigma \Delta$ ) modulator was carried out to define electrical characteristics of an Analog Building Block (ABB), specifically a fully differential OTA. A set of experiments based on analytical models was defined to analyze the overall performance of the Switched Capacitor (SC)  $\Sigma\Delta$ modulator in order to translate the design considerations into a set of values that the design at transistor level can be established by the desired performance of the chosen architecture. In accordance with this design strategy, a fully differential CFCFC OTA was designed according to design rules of a 130nm CMOS process. Simulation results show that an open-loop gain  $A_0 = 60$ dB, and unity-gain bandwidth  $f_{0dB} = 1.0$ GHz are enough to obtain a Signal-to-Noise Ratio (SNR) of 68dB (±1dB) when this OTA is added to the DT  $\Sigma\Delta$  modulator. Furthermore the hand-made small-signal analysis of the chosen OTA topology allow us to obtain an analytic design model useful to correlate not only CADENCE results, but also to identify the most important parameters affecting the frequency response.

Keywords—High level simulation,  $\Sigma\Delta$  modulation, OTA, small-signal analysis, analog design, teaching.

# I. Introduction

The design of analog systems consists of three basic steps: architecture selection, establishment of analog building specifications and minimization of the circuit non-idealities effects on the whole system performance [1]. As described in [2] the individual analysis strategy is not the most suitable one as these design steps are deeply correlated, which means that a unique fully-integrated analysis must be developed. In such an approach all design considerations are treated at the highest level of abstraction because of the need to reduce simulation time, mainly when the chosen architecture is analyzed at transistor level. In addition, high level simulation allows the designer to find the desired performance of the selected architecture, which can be converted into a set of values, so that the parameters of the transistor-based circuits can be established directly.

D. Calderón-Preciado, J. G. García-Sánchez, F. Sandoval-Ibarra Cinvestav Guadalajara Unit México [dcalderon, ggarcia,

E. Ch. Becerra-ÁlvarezUniversidad de GuadalajaraMéxico

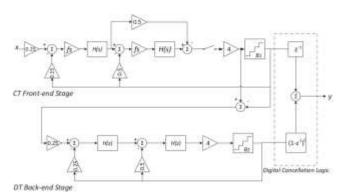

Figure 1. Modulator Architecture

In this scenario the design of an analog system consists of solving a unique problem: the development of a behavioral model that not only minimizes simulation time but also reflects the effects of the so called circuit non-idealities [3]. In this paper, actually a work in progress, SIMSIDES-based behavioral modeling [4] of a 4<sup>th</sup> order Hybrid  $\Sigma\Delta$  modulator is design fully-differential a Operational Transconductance Amplifier (OTA) in order to satisfy the design requirements of the DT back-end stage shown in Fig. 1. From behavioral simulation a set of values were found such that the parameters of the transistor-based circuits have been established according to the desired performance of the chosen architecture, where the function of each Processing Basic Block (PBB) is easily identified (see Fig. 1). According to the simulation conditions shown in Table I, the unity-gain bandwidth of the OTA must be at least five times the required sampling frequency value, i.e.  $f_{0dB} = 1GHz$ . Also, both low and high-frequency small-signal analysis were carried out in order to attain a better understanding of the OTA topology.

# п. Behavioral Modeling as a starting point in an OTA design

The modulator loop-filter is a 4<sup>th</sup> order proposal, specifically a 2-stage (2-2) architecture, where the front-end is a CT implementation and the back-end a DT proposal. The strategy behind the high level simulation of the hybrid  $\Sigma\Delta M$  has been defined as follows: 1) the weights of both modulators were obtained from numerical analysis, 2) for simulation purposes the front-end was assumed to be an ideal system (non-idealities were not taken into account), and 3) the back-end is firstly assumed as an ideal design and then non-idealities are included in order to quantify their effect on the system performance, by comparing both scenarios. With the

TABLE I. SIMULATION CONDITIONS

| Ouantizer    | Bias                               | ±1.2V      |

|--------------|------------------------------------|------------|

| Quantizer    | Number of levels                   | 3          |

| Input Signal | Amplitude                          | -10dB      |

| input signai | Frequency, $f_i$                   | 991.234kHz |

|              | Bandwidth                          | 10MHz      |

|              | Sampling frequency, f <sub>s</sub> | 200MHz     |

TABLE II. SELECTED PARAMETERS

|               | $I_O$        | 0.3mA |

|---------------|--------------|-------|

|               | $g_m$        | 3mS   |

| SC Integrator | $A_0$        | ≥60dB |

|               | $R_{on}$     | 250Ω  |

|               | Output Swing | ±0.6V |

help of SIMSIDES (SIMulink-based SIgma-DElta Simulator) the strategy mentioned above was carried out to obtain a set of specific parameters that must be translated into a transistor-based implementation.

In order to define the design specifications of each PBB is of paramount importance to state a list including the most important sources of non-idealities that affect the expected performance of the whole design. It is well known that the physical parameters affecting the overall behavior of the SC integrator are in high percentage the open-loop gain  $(A_0)$ , the unity-gain bandwidth  $(f_{OdB})$ , the input transconductance  $(g_m)$  and the maximum output current  $(I_O)$  of the OTA [2], [5]. Furthermore, the performance of SC integrator circuits are affected by several other OTA non-idealities, such as slew-rate and settling time, which can be minimized depending on the type of OTA used. According to simulation results, a set of specific characteristics for the OTA were found which are shown in Table II.

# ш. OTA Design

#### A. OTA and CMFB Architecture

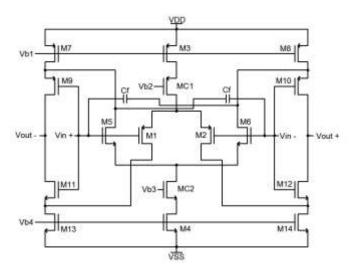

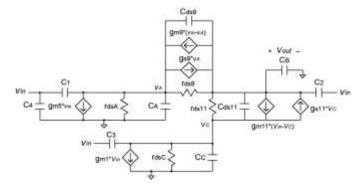

Differential signal processing is the key for designing a robust implementation, thus a fully-differential OTA has been chosen to build a SC integrator. A differential implementation reduces the common mode noise due to power supply and substrate, clock feedthrough, charge injection and also eliminates even-order harmonic components [6]-[7]. Because of the system's sampling frequency (200MHz), an OTA with a unity-gain bandwidth,  $f_{0dB} = 1GHz$ , and a phase margin between 45°-60° that provides good settling behavior [8]-[9], must be designed. The chosen OTA architecture is a Complementary Folded Cascode Feedforward Compensated (CFCFC) shown in Fig. 2, which is very similar to that analyzed in [6], the difference between both proposals resides in the floating capacitor,  $C_f$ . In this proposal, cascode stages

Figure 2. CFCFC OTA [9], [13]

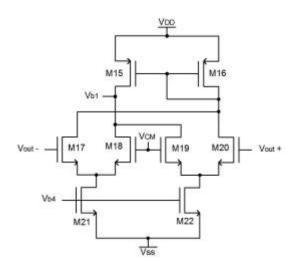

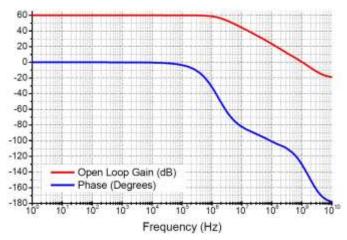

provide high gain and fast operation even when low power supply is used (as low as  $\pm 1.2V$ ) [9]. The feedforward technique lends itself for low supply folded cascode amplifiers since the DC bias for the cascode and input transistors is the same, that is the middle point between the positive and negative voltage supply (in this case 0V), allowing the gate connection. The floating capacitor,  $C_f$ , is used to feed and change the phase of the input signal forward to the cascode node that provides the input pole cancellation because of the source resistance at the input [10]. The OTA bandwidth is maximized by increasing the transconductance of the input transistors, which is achieved using wide devices and ensuring that the input transistor bias current is larger than the bias of the cascode transistors [8]. The Common Mode FeedBack (CMFB) block senses the common mode voltage at the amplifier's outputs (ideally not the differential mode voltage), process it, and then a voltage is feedback to the amplifier to fix the DC current flowing through the output stage; this process also changes the common mode voltage to a preset value, normally analog ground to maximize the output signal swing. The CMFB implemented (see Fig. 3) when compared to other architectures surpasses them in performance due to its good linearity, high sensitivity to common mode signals and small parasitic capacitance, trading off chip area and power consumption [11]-[12]. The OTA open-loop frequency response is displayed in Fig. 4.

# B. Low-frequency small-signal analysis

For the CFCFC OTA the DC gain is the product of the effective transconductance and the output resistance

$$A_0 = r_{out} * g_{m,eff} \tag{1}$$

The low-frequency small-signal equivalent circuit is analyzed to obtain a mathematical model where the highest impact transistor level parameters are easily identified. In the simplest analysis several considerations are usually made where the source/bulk voltage and conductances are neglected. In this paper, bulk transconductance is taken into account in order to obtain a correct model for the open-loop gain.

Figure 3. Common Mode Feedback Circuit [12]

Figure 4. CFCFC AC response

Table III shows the comparison results between several hand-made small-signal analyses, where the last column represents the error when compared to CADENCE. As can be seen, if all the small-signal components are taken into account, the difference between the analytic results and SPICE results is less than 1%.

# c. High-frequency small-signal analysis

Top level simulations using transistor level circuits usually take a long time, which is why suitable equivalent models are needed. The most important element of a Switched Capacitor

TABLE III. LOW-FREQUENCY SMALL-SIGNAL COMPARISON

| Considerations                          | $r_{out}(\Omega)$ | $g_{m,eff}(mS)$ | $A_{\theta}(\mathbf{dB})$ | $\varepsilon_r(\%)$ |

|-----------------------------------------|-------------------|-----------------|---------------------------|---------------------|

| $\checkmark V_{SB}, \checkmark g_{ds}$  | 32997             | 30.2            | 59.97                     | 0.338               |

| $\mathbf{X}V_{SB}$ , $\mathbf{J}g_{ds}$ | 29592             | 29.9            | 58.95                     | 11.38               |

| $\mathbf{X}V_{SB}, \mathbf{X}g_{ds}$    | 23126             | 29.4            | 56.64                     | 32.08               |

| [9]                                     | 25883             | 32.4            | 58.37                     | 17.06               |

Figure 5. CFCFC High-Frequency differential half Small-Signal Model

integrator filter is its amplifier, therefore if an equivalent circuit is implemented, the simulation time could be reduced significantly. The high-frequency differential half equivalent circuit is shown in Fig. 5. The capacitances and conductances of the circuit are related to the transistors by the following equations:

$$C_A = C_{db5} + C_{db7} + C_{gd7} + C_{sb9} + C_{ds5} + C_{ds7}$$

(2)

$$C_B = C_{db9} + C_{db11} + C_{gd17} + C_{gs17} + C_L$$

(3)

$$C_C = C_{db1} + C_{db13} + C_{gd13} + C_{sb11} + C_{ds1} + C_{ds13} \quad (4)$$

$$C_1 = C_{\alpha d5} + C_{\alpha s9} \tag{5}$$

$$C_2 = C_{od9} + C_{od11} \tag{6}$$

$$C_3 = C_{gd1} + C_{gs11} (7)$$

$$C_4 = C_{es1} + C_{es5} \tag{8}$$

$$r_{dsA} = r_{ds5} \parallel r_{ds7} \tag{9}$$

$$r_{dsC} = r_{ds1} \parallel r_{_{ds13}} \tag{10}$$

where  $C_L$  is the load capacitance at the output terminal, and the other capacitive and resistive terms have their usual meaning.

The response obtained when solving the equivalent circuit in Fig. 5 presents great consistency when compared to that of CADENCE (see Fig. 6), allowing its use to reduce significantly the simulation time of the system.

#### D. Other Results

The OTA has been designed according technological design rules of a 130nm CMOS process. A summary of the simulation results is shown in Table IV whereas Table V displays the transistor dimensions of both OTA and CMFB. The results achieved by the CFCFC OTA fulfill not only the performance listed in Table II, but also the expected performance at system level depicted in Table I.

Figure 6. Transistor Level Simulation vs Circuit Equivalent Model

| TABLE IV | SIMILI ATION | PECH TC |

|----------|--------------|---------|

|     | $I_O$      | 0.311mA  |

|-----|------------|----------|

|     | $f_{OdB}$  | 1.047GHz |

| ОТА | $A_0$      | 60dB     |

| V   | $C_L$      | 2.5pF    |

|     | $\Phi_{M}$ | 48.5°    |

|     | $P_S$      | 11.82mW  |

TABLE V. TRANSISTOR'S SIZES AND CAPACITORS VALUES

|      | M1-M2   | 1371:1 |

|------|---------|--------|

|      | M3      | 492:1  |

|      | M4      | 64:1   |

|      | M5-M6   | 416:1  |

| OTA  | M7-M10  | 504:1  |

| OIA  | M11-M12 | 165:1  |

|      | M13-M14 | 56:1   |

|      | MC1     | 614:1  |

|      | MC2     | 75:1   |

|      | Cf      | 2.5pF  |

|      | M15-M16 | 712:1  |

| CMFB | M17-M20 | 44:1   |

|      | M21-M22 | 56:1   |

# v. Conclusions

The main advantage of high level simulation is that all the design considerations are converted into a set of values, where the most important parameters of the transistor-based circuits can be easily established according to the desired performance

of the chosen architecture which allows the designer to identify key parameters. As shown in Table II, the simulation process has resulted in feasible design values, that if fulfilled, represent an equivalent number of bits (ENOB) of 10.46. However, several parameters still must be optimized, such as parasitic capacitance, integrator settling behavior and current leakage [14]. With the help of SIMSIDES, a system design was carried out in order to firstly obtain a group of specific parameters that show us the viability of a transistor-based system synthesis. The OTA architecture was secondly designed and simulated at transistor level to illustrate the proposed design methodology. Also, on the one hand, the results due to low-frequency small-signal analysis, when considering all of the transistor components, are highly accurate and allow the designer which parameters must be redesigned. The same is true, if needed, to redesign open-loop gain or output resistance. On the other hand, high-frequency small-signal models help us to reduce the simulation time compared to transistor level circuits. Finally, it is important to underline that analog design is an engineering discipline supported by laws of physics, where some of them are included into this design methodology.

#### Acknowledgment

This work is supported by the Mexican Council of Science and Technology (CONACyT) under grant 169660.

### References

- [1] Naveen Chandra and Gordon W. Roberts, Top-down analog design methodology using matlab and simulink. *International Symposium on Circuits and Systems (ISCAS)*, volume 5, pp. 319-322, 2001.

- [2] J.G. García-Sánchez, D. Calderón-Preciado, F. Sandoval-Ibarra and José M. de la Rosa, Behavioral modelling of a 4<sup>th</sup> order LP ΣΔ modulatortowards the design of a hybrid proposal. 2014 IEEE 5<sup>th</sup> Latin American Symposium on Circuits and Systems(LASCAS), pp. 1-4, 2014.

- [3] Scott D. Kulchycki, Roxana Trofin, Katelijn Vleugels and Bruce A. Woodley, A 77dB dynamic range, 7.5MHz hybrid continuous time/discrete time cascaded modulator, *IEEE Journal of Solid State Circuits*, pp. 796-804, 2008.

- [4] Jesús Ruiz-Amaya, J.M. de la Rosa, Francisco V. Fernández, Fernando Medeiro, Rocío del Río, Belén Pérez-Verdú and Angel Rodríguez-Vázquez, High-level synthersis of switched-capacitor, switched-current and continuous-time ΣΔ modulators using SIMULINK-based time-domain behavioral models, IEEE Transactions on Circuits and Systems 1: Regular Papers, 52(9): 1795-1810, 2005.

- [5] Rocío del Río, CMOS cascade Sigma-Delta modulators for sensors and telecom: error analysis and practical design, Springer, 2006.

- [6] H. Lampinen and O. Vainio, A low-voltage, multibit ΣΔ modulator for wideband applications, IEEE Third International Workshop on Design of Mixed-Mode Integrated Circuits and Applications, pp. 138-142, 1999.

- [7] S. Setty and C. Tomazou, N-Folded cascode technique for high frequency operation of low voltage opamps, *Electronics Letters*, pp. 955-957, 1996.

- [8] David A. Jhons and Ken Martin, Analog integrated circuit design, John Wiley & Sons, 2008.

- [9] H. Lampinen and O. Vainio, An optimization approach to designing OTAs for low-voltage ΣΔ modulators, *IEEE Transactions on Instrumentation and Measurement*, pp. 1665-1671, 2001.

- [10] S. Setty and C. Tomazou, Feedforward compensation techniques in the design of low-voltage opamps and OTAs, Proceedings of the 1998 IEEE

International Symposium on Circuits and Systems, volume 1, pp. 464-467, 1998.

- [11] S. Mallya and J. H. Nevin, Design procedures for a fully differential folded-cascode CMOS operational amplifier, *IEEE Journal of Solid-State Circuits*, pp. 1737-1740, 1989.

- [12] P. Wu, R. Schaumann and P. Latham, Design considerations for common-mode feedback circuits in fully-differential operational transconductance amplifiers with tuning, *IEEE International Symposium* on Circuits and Systems, pp. 1363-1366, 1991.

- [13] S. Setty and C. Tomazou, A new architecture for low voltage CMOS operational amplifiers, *Proceedings of 1997 IEEE International Symposium on Circuits and Systems*, volume 1, pp. 225-228, 1997.

- [14] A. Pugliese, F. A. Amoroso, G. Cappuccino and G, Cocorullo, Effect of the integrator settling behavior on SC ΣΔ modulator characteristics: a theoretical study, 2<sup>nd</sup> International Conference on Signals, Circuits and Systems, pp. 1-6, 2008.

About Author (s):

**Daniel Calderón Preciado** was born in Culiacán, México. He received the B.E. degree in Electronics from Instituto Tecnológico de Culiacán in 2012 and the M.S. degree in electrical engineering from the Research and Advanced

Studies Center (CINVESTAV), Guadalajara, México. He is currently working towards his D. Sc. degree in electrical engineering at CINVESTAV. His main areas of interest are Sigma-Delta Modulation, A/D converters and CMOS amplifier design.

**J. Gerardo García-Sánchez** received the M.S. degree in electrical engineering from the Research and Advanced Studies Center (CINVESTAV), Guadalajara, Mexico, and the Master in

Microelectronics degree from the University of Seville, Spain, in 2008 and 2010, respectively. He is currently working toward the D. Sc. degree in electrical engineering at CINVESTAV. His main areas of interest are in the field of Sigma-Delta analog-to-digital converters, including analysis, behavioral modeling, and design of such circuits.

**Federico Sandoval-Ibarra** was born in San Luis Potosí, Mexico. He received the B.E. degree in Physics-Electronics from Universidad Autónoma de San Luis Potosí, Mexico, in 1988, and the D. Sc. degree in electronics from Instituto Nacional de

Astrofísica, Óptica y Electrónica (INAOE), Mexico, in 1998. From 1991 to 1996, he was with the Microelectronics Laboratory at INAOE as a researcher, where he was developing wet-etching techniques for designing silicon-based microsensors. In 1997, he was with CNM-Bellaterra (Spain), as a visiting researcher being involved in the development of surface micromachining techniques to design a fully-integrated microphone. In 1999, he joined CINVESTAV-Guadalajara Unit, Mexico. His research areas include the design of low-noise analog circuits, mixed-mode circuits design for RFID applications and the physical origin of electronic noise. He is presently working on the design of A/D converters based on Hybrid ΣΔ Low-Pass Modulators for multi-standard applications.

Edwin Christian Becerra Alvarez, received the B.S. degree on Communications and Electronic Engineering from the University of Guadalajara, Mexico in 2004, the M.S. degree on Electric Engineering from CINVESTAV, Mexico in 2006

and the D. Sc. degree on Microelectronics from the University of Seville, Spain in 2010. Since 2010 he is working in the University of Guadalajara and his current research interests are on CMOS RF circuits.