Volume 4: Issue 1

Publication Date: 09 January 2014

# Energy Comparison of Different NOC Routers

Biman Debbarma

S. N. Pradhan

Anupam Jamatia

Abstract— Energy consumption in an SOC is increasing as the level of integration is increasing. NOC routers are responsible for consuming major part of the energy consumed by the system. This paper shows a comparison of energy consumption among different routing techniques.

Keywords—NOC, routing, energy, packet injection rate.

#### Introduction

In the last decade interconnecting networks on chip have become an essential part of the system on chip architecture for efficient communication between various IP modules. In [1] it was shown that a major part of the energy consumption is due the NOC routers. Though the energy consumption depends on various factors, we have compared the energy consumption of NOC routers among some routing techniques at various packet injection rate.

Rest of the paper is organized as follows: in section II various routing techniques are discussed. Section III shows some related works in this field. The simulation result is shown in section IV.

# **Various Routing Techniques**

## A. XY Routing

In XY routing [2], packets are first routed in the horizontal (X) direction and then in the vertical (Y) direction. This type of routing is deterministic and it is deadlock free as well as livelock free. Here the XY coordinates of the routers are their addresses. The address on the header flit is compared with the address of the router. If they match, the flits go to the core of the router. If only X coordinate matches it moves to the Y direction until it reaches its destination router. It has the disadvantage of mid network congestion.

Biman Debbarma bimandebbarma75@gmail.com

S. N. Pradhan sambhu.pradhan@gmail.com

Anupam Jamatia anupamjamatia@gmail.com

National Institute of Technology, Agartala India

## B. West First Routing

In west first routing [3], a turn to the west direction is not allowed later i.e. first the movement should be in the west direction and after that turns are allowed in north, south and east only. The path may be minimal or non minimal.

## c. Negative First Routing

Two 90 degrees turn can also be avoided by negative first routing [3]. Here, turns towards negative direction i.e. west (negative X) and south (negative Y) are taken first and then east or north turns are taken depending upon the destination address.

## D. Odd Even Routing

This is a deadlock free algorithm where in even columns east to north and east to south turns are not allowed. Similarly in odd columns north to west and south to west turns are prohibited. Odd Even routing avoids the usage of virtual channels which can consume a lot of energy.

## E. DyAD Routing

DyAD or Dynamically Adaptive and Deterministic routing was proposed by Hu et al. in [4]. In this type of routing the routing technique may be deterministic (in this case it is XY routing) or adaptive (minimal odd even routing) depending upon the traffic congestion. This threshold value of traffic congestion is dependent upon the user. Two types of routing techniques are used because of their advantages at different situations. Deterministic routers are easy to implement whereas if packet injection rate increases, adaptive routing gives better throughput.

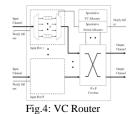

# F. Fully Adaptive Routing Algorithm

Fully adaptive means the path of the flits is not predetermined. Depending upon the traffic congestion decisions are made in which direction the flits should move. This requires the usage of virtual channels. Virtual channels are extra buffers which have to be used to avoid congestion in a particular router. Flits entering into a router are assigned a virtual channel by a VCA (Virtual Channel Arbiter). SA (Switch Allocator) and Crossbar Switch take the flits to the destination output port. As the there is no prescribed path for the flits, sometimes the flits take lot of time to reach the destination even in some cases it may never reach there.

The following figures show various routing techniques.

Publication Date: 09 January 2014

Fig. 1: XY Routing

Fig.2: West First Routing

Fig. 3: Negative First Routing

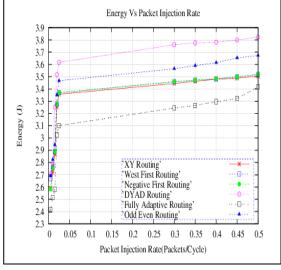

Fig. 5: Energy Vs Packet injection rate plot

#### ш. **Related Work**

Power aware NOC design was first discussed in [5] by Patel et al. Low-swing on chip links was discussed in [6] and low power link design was considered in [7]. Dynamic voltage scaling [8], Power-Herd[9], run-time power gating using look ahead [10] etc are discussed in literature. Hale et al discussed segment gating for static energy reduction in [11]. Matsutani et al. formed slow silent virtual channel to reduce leakage and dynamic power [12].

#### **IV. Simulation Result**

# A. Experimental Setup

We have simulated the energy in Jule for different routing algorithms at different packet injection rates (packets/cycle). The simulation was done in SystemC based Noxim software. Time distribution of traffic was Poisson and traffic generation was random. Here an 8X8 mesh type NOC structure was used. The packet size was taken to be 8 flits.

# B. Experimental Result

The experimental results are shown in fig 5. Packet injection was varied from 0.005 to 0.5 and the corresponding energy readings were observed and plotted. The energy readings are of the order of e-05 which is not shown in the graph. It can observed from fig. 5 that XY, West first and Negative first routing algorithms have almost same energy consumption characteristics with increasing packet injection rate. Fully adaptive routing has the least energy consumption whereas DyAD routing has the highest energy consumption. But at the same time from table I it is seen that DyAD routing has higher average throughput compared to some other algorithms.

Table I

| sl. no. | Routing Algorithm | Packet Injection Rate (packet/cycle) |      |      |

|---------|-------------------|--------------------------------------|------|------|

|         |                   | 0.1                                  | 0.3  | 0.5  |

| 1.      | XY                | .013                                 | .013 | .013 |

| 2.      | West First        | .014                                 | .014 | .014 |

| 3.      | North Last        | .014                                 | .014 | .014 |

| 4.      | Odd Even          | .014                                 | .014 | .014 |

| 5.      | DyAD              | .015                                 | .015 | .015 |

Average Throughput(flits/cycle/IP) table

## Acknowledgment

We are thankful to our organization for extending full support to us. We also thank Noxim developers because of whom we could simulate the energy consumption for different routers.

#### References

- [1] H. Kim, P. Ghoshal, B. Grot, P. V. Gratz and D. A. Jimenez, "Reducing Network-on-chip energy consumption Lipschitzthrough spatial speculation" NOCs' 11 May 1-4, 2011, Pittsburg, PA, USAACM 978-1-4503-0720-8.

- [2] M. Dehyadgari, M. Nickray, A. Afzali-kusha, Z. Navabi, "Evaluation of pseudo adaptive XY routing using an object oriented model for NOC" The 17<sup>th</sup> International Conference on Microelectronics, 13-15 December 2005.

- [3] C. J. Glass and L. M. Ni, "The turn model for adaptive routing" Journal of the Associasion for Computing Machinery, vol. 41, no. 5, September 1991 pp. 874-902.

- [4] J. Hu, R. Marculescu, "DyAD- Smart routing for networks-on-chip" Proceedings, 41st Design Automation Conference, 2004, pages 260=263.

- [5] C. S. Patel, S. M. Chai, S. Yalamanchili, and D. E. Schimmel, "Power constrained design of multiprocessor interconnect networs" Proc. International Conference on Computer Design, pages 408-416, 1997.

- [6] H. Zhang, V. George, and J. M. Rabacy, "Low –swing on-chip signaling techniques: Effectiveness and robustness" IEEE Transactions on VLSI Systems, 8(3):264-272, 2000.

Publication Date: 09 January 2014

- [7] M. J. E. Lee, W. J. Dally, and P. Chiang, "Low power area efficient high-speed I/O circuit techniques: IEEE Journal of Solid-State Circuits, 35(11):1591-1599, 2003.

- [8] L. Shang, L. S. Peh, and N. K. Jha, "Dynamic voltage scaling with links for power optimization for interconnnection networks" In Proc. International Symposium on High Performance Computer Architecture, pages 91-102, 2003.

- [9] L. Shang, L. S. Peh, and N. K. Jha, "Powerherd: Dynamically satisfying peak power constraints in interconnection networks' In proc. International Conference on Supercomputing, pages 98-108, 2003.

- [10] Hiroki Matsutani, Michihiro Koibuchi, Hiroshi Nakamura, and Hideharu Amano "Run time power gating techniques for low power on chip networks" IEEE 978-1-4244-1922-7/08, 2008.

- [11] K. C. Hale, B. Grot, and S. W. Keckler, "Segment gating for static energy reduction in networks on chip: NoCArc 2009 — December 12, 2009, New York, New York, USA

- [12] Hiroki Matsutani, Michihiro Koibuchi, D. Wang, and Hideharu Amano, "Adding slow silent virtual channels for low power on chip networks: Networks-on-Chip, 2008. NoCS 2008. Second ACM/IEEE International Symposium on 7-10 April, 2008.

Biman Debbarma is presently working as Assistant Professor at Electronics & Communication Engineering Department, National Institute of Technology Agartala, received B.Tech India. (NIT Jamshedpur), M.Tech (NIT, Agartala), currently pursuing Ph.D.(VLSI) at NIT Agartala. His research interests include Network on Chip, Image Processing etc. He has 7 years of academic experience Agartala), currently pursuing Ph.D.(VLSI) at NIT Agartala. His research interests include Network on Chip, Image Processing etc. He has 7 years of academic experience.

Sambhu Nath Pradhan received Ph.D. from Indian Institute of Technology and M.E. from Bengal Engineering and Science University in 2010 and 2004 respectively. He is currently working as an Assistant Professor in the Department of ECE, National Institute of Technology Agartala. His research interest include low power design and testing and thermal aware design.

Anupam Jamatia is presently working as Assistant Professor at Computer Science & Engineering Department, National Institute of Technology Agartala, India. His research interests include Computer Networks, Wireless Networking etc. He has 7 years of academic experience.