## Delay Analysis in Carbon Nanotube Bundle Interconnect For VLSI Design

[Devenderpal Singh and Mayank Kumar Rai]

Abstract: This paper proposes to study the performance of carbon nanotube bundle in terms of delay as a VLSI interconnect at 32nm technology node. Output waveform and 90% propagation delay are analytically determined and compared with SPICE simulation result. Alpha power law model is used for representing the transistors of CMOS driver. SPICE simulation result reveals that delay increases with increase in length of interconnect.

Keywords: Carbon Nanotubes, Interconnect, Propagation Delay, L-segment RLC

#### 1. Introduction

The integrated chips are mostly made of conducting wires, that are called VLSI interconnects. Until 180nm technology node aluminum wires were used as interconnects but as technology scales down aluminum interconnect suffers from electro migration because its current density is very low [1]. Later copper interconnects were preferred over aluminum interconnect because of its high conductivity and high current density. Due to continuous reduction in feature size copper interconnect faced problems of grain boundary effect and electro migration [1-2]. To overcome these problems Carbon Nanotube (CNT) based interconnects are found to be better alternative for copper interconnects at lower technologies [3].

CNTs are formed by rolling up the graphite sheets in the form of cylinder with diameter in the order of a nanometer. Due to its long electron mean free path (in the order of micrometer), CNT has high current density and lower resistivity than copper [4]. CNTs can be either metallic or semiconductor. Metallic CNTs are more attractive interconnects due to their high thermal conductivity [5].

Devenderpal Singh ECED, Thapar University India devs.singh90@gmail.com

Mayank Kumar Rai ECED, Thapar University India mkrai@thapar.edu п. Piecewise Transient Analysis

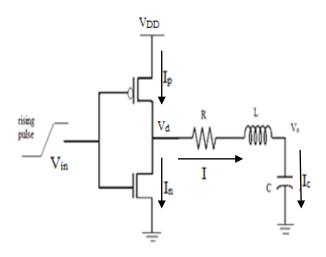

A CMOS inverter with L segment RLC circuit of 1mm length of interconnect is shown in fig.1. The alpha-power law model [17] is used to represent the transistor current. The drain current is given in following equation for different regions of operations-

CNTs are of two types-Single walled Carbon Nanotubes (SWCNT) and Multiwalled Carbon Nanotubes (MWCNT). SWCNT consists of a single graphite sheet in cylindrical form and MWCNT consists of multiple concentric cylinders [6]. SWCNT has large resistance, so it is not a good choice for interconnect. So, a parallel connection of a large number of SWCNTs can be used in which four conducting channels are in parallel. Such SWCNT bundle has lower resistance than Copper interconnect[7].

Interconnect delay is the key factor to determine the performance of a chip. In the past, generally RC delay models were used. Dartu et al. [8] startred with a RC  $\pi$ -model for the timing analysis of RC interconnect. Elmore delay model [9] was used to estimate the signal delay through RC. But at higher frequencies, wire inductance starts to play a role on the chip. So RC model was no longer being adequate and RLC model was proposed. Friedman et al. [10] analyzed the inductance effect on RLC interconnect. An analytical solution for the output waveform for CMOS gate driving RLC line was presented [10]. K Banerjee et al. [11-12] proposed an optimization technique for Lumped RLC interconnect to analyze the effect of line inductance on circuit performance. J A Davis and J D Meindl [13-16] described the transient response of distributed RLC line in which CMOS inverter was replaced by resistor. In this paper simple output voltage models in four different regions are presented to extract output waveform for L segment RLC.

The rest of this paper is given as follows: Section II presents the piecewise transient model while in section III, transient results in all four regions are compared to the SPICE simulation result. The impedance analysis and effect of interconnect length on delay are also observed in section III. Finally section IV draws necessarily conclusion.

$$I_{d} = \left\{ \begin{array}{ll} 0; & V_{\text{GS}} \leq V_{\text{To}} \text{: cut-off region} \\ k_1 (V_{\text{GS}} - V_{\text{TO}})^{\alpha/2} V_{\text{DS}}; & V_{\text{DS}} < V_{\text{DSAT}} \text{: linear region} \\ k_s (V_{\text{GS}} - V_{\text{TO}})^{\alpha}; & V_{\text{DS}} \geq V_{\text{DSAT}} \text{: saturation region} \end{array} \right.$$

Here  $\alpha$  is called velocity saturation index;  $k_l$ ,  $k_s$  are the transconductance parameters in linear and saturation region of the transistor respectively,  $V_{DSAT}$  is drain-saturation voltage and  $V_{To}$  is threshold voltage at zero bias.

Figure 1. An equivalent model of CMOS gate driving L segment RLC circuit of interconnect

In this case the analytical expression for output voltage is obtained in different four regions of operations of the transistor for fast input ramp [18].

Applying KCL at drain of nmos-

$$I_n + I - I_p = 0 \tag{1}$$

An analytical expression for output voltage is calculated for rising input ramp. During rising input ramp, output node is discharged that means nmos transistor will be conducting. So during rising transition, the effect of pmos transistor can be neglected due to short circuit current [17]  $(I_p = 0)$ .

So from equation (1)-

$$I_n + I = 0$$

(2)

Region 1 ( $0 < t < t_1$ ): The nmos transistor is in cut off during this region. This region extends until time  $t_1$ , when  $V_{GS} = V_{To}$ . So putting  $I_n = 0$ , equation (2) reduces to-

$$I = 0$$

,  $I_c = 0$ ,  $C \frac{dV_o}{dt} = 0$

Here initial condition is-  $V_o(0) = V_{DD}$

The output  $V_0$  remains  $V_{DD}$  upto time  $t_1$ .

Region 2  $(t_1 < t < \tau)$ : During this region nmos operates in saturation region. Here  $\tau$  is the rise time of input pulse. The current through nmos transistor during saturation region is given as-

$$\begin{split} &I_n = k_s (V_{GS} - V_{To})^{\alpha} \\ &I_n = k_s \left(\frac{V_{DD}}{\tau} t - V_{To}\right)^{\alpha} \end{split}$$

From equation (2)-

$$\begin{aligned} k_s \left( \frac{V_{DD}}{\tau} t - V_{To} \right)^{\alpha} + I &= 0 \\ k_s \left( \frac{V_{DD}}{\tau} t - V_{To} \right)^{\alpha} + C \frac{dV_o}{dt} &= 0 \end{aligned}$$

$$\text{here } k_s = \frac{I_{DO}}{(V_{DD} - V_{TH})^{\alpha}}$$

(3)

To solve equation (3), the term including  $\alpha$  is solved using second order taylor series expansion at  $t=\tau/2$  (here  $V_{in}=V_{DD}/2$ ) as-

$$\frac{k_s \left(\frac{V_{DD}}{t} t - V_{To}\right)^{\alpha}}{C} = a_0 + a_1 t + a_2 t^2$$

So the solution of differential equation (3) is as -

$$V_0(t) = K - a_0 t - \frac{a_1}{2} t^2 - \frac{a_2}{3} t^3$$

Here K is integration constant and value of K is calculated using initial condition  $V_o(0) = V_{DD}$

Region 3 ( $\tau < t < t_2$ ): At this region the input ramp has reached its final value and nmos transistor is still operates in saturation region. The current through nmos transistor is given as [17]-

$$I_n = k_s (V_{DD} - V_{To})^{\alpha}$$

Now differential equation becomes-

$$C\frac{dV_o}{dt} + k_s(V_{DD} - V_{To})^{\alpha} = 0$$

(4)

The solution of above differential equation is-

$$V_o(t) = K_1 - K_2 t$$

Here K<sub>1</sub> is integration constant and

$$K_2 = \frac{k_s}{c} (V_{DD} - V_{To})^{\alpha}$$

The nmos transistor exits saturation at time  $t_2$ . Time  $t_2$  is calculated by equating drain-source voltage and drain-saturation voltage of nmos transistor [17].

$$V_d(t_2) = V_{DSAT}$$

$$RI + L\frac{dI}{dt} + V_o = V_{DSAT}$$

(5)

Here

$$I=C \frac{dV_o}{dt}$$

and  $V_{DSAT}=\frac{k_s}{k_l}(V_{GS}-V_{TN})^{\alpha/2}$

Region 4 ( $t>t_2$ ): During this region nmos transistor operates in linear region and current through the transistor is given as-

$$I_n = k_l (V_{DD} - V_{TO})^{\alpha/2} V_d$$

Now differential equation becomes-

$$C\frac{dV_0}{dt} + k_1(V_{DD} - V_{TO})^{\alpha/2} V_d = 0$$

(6)

Here

$$V_d = RI + L\frac{dI}{dt} + V_o$$

$k_1$  is calculated by  $I_{DS} - V_{DS}$  characteristics of transistor and is given as [17]-

$$k_l = \frac{l_{Do}}{v_{Do} (v_{DD} - v_{TH})^{\alpha/2}}$$

Equation (6) becomes-

$$\frac{d^{2}V_{0}}{dt^{2}} \left( LC k_{l} (V_{DD} - V_{To})^{\alpha/2} \right) + \frac{dV_{0}}{dt} \left( C + RC k_{l} (V_{DD} - V_{To})^{\alpha/2} \right) + k_{l} (V_{DD} - V_{To})^{\alpha/2} V_{o} = 0$$

So the solution of differential equation (6) is-

$$\begin{array}{l} V_o(t) = 0.45 * \frac{(-\kappa_2 * \sqrt{M} - \kappa_2^2 + 4 * \kappa_3 * \kappa_1)}{-M} e^{-(\kappa_2 - \sqrt{M})t/2 * \kappa_1} + 0.45 * \\ \frac{(\kappa_2 * \sqrt{M} - \kappa_2^2 + 4 * \kappa_3 * \kappa_1)}{-M} e^{-(\kappa_2 + \sqrt{M})t/2 * \kappa_1} \end{array}$$

Here

$$K_1 = LC k_l (V_{DD} - V_{To})^{\alpha/2}, K_2 = (C + RC k_l (V_{DD} - V_{To})^{\alpha/2})$$

$K_3 = k_l (V_{DD} - V_{To})^{\alpha/2} And M = K_2^2 - 4 * K_3 * K_1$

### **III. Results and Discussions**

# A. Comparison Of Analytical and Simulation Result

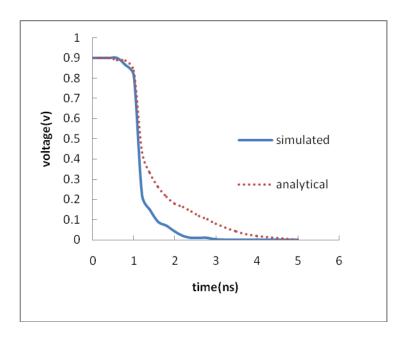

Figure 2. Comparison of analytical and simulated result of L segment RLC line for rising input pulse.

Figure 2 shows the transient response of CNT bundle for 1mm length of interconnect. The above graph reflect the difference between analytical and simulation result of L segment RLC circuit of 1mm length of interconnect.. It is observed that for fast ramp input signal analytical result in terms of output voltage accurately matched with simulation in saturation and some deviation is found in linear region.

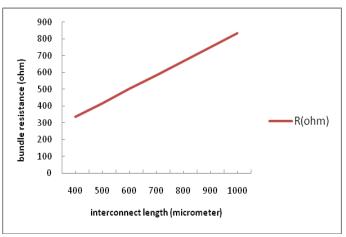

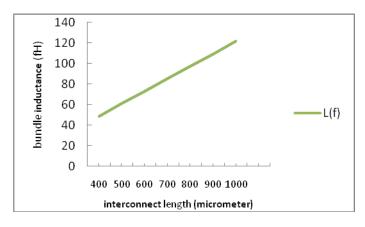

## B. Impedance Analysis Of SWCNT Bundle Interconnect

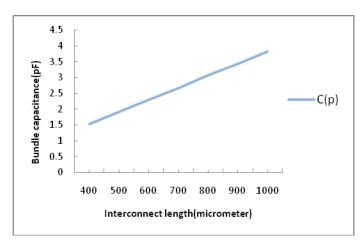

The effect of impedance parameters (R, L, C) on interconnect length are shown in Fig.3.The circuit impedance parameters are calculated from the models available in [6-7]. Result shows that the value of impedance parameters R, L, C increases with increase in interconnect length as shown in Fig. 3(a), 3(b) and 3(c).

Figure 3 (a). Variation of bundle resistance as a function of interconnect length at 32 nm technology node.

Figure 3 (b). Variation of bundle inductance as a function of interconnect length at 32 nm technology node.

Figure 3 (c). Variation of bundle capacitance as a function of interconnect length at 32 nm technology node.

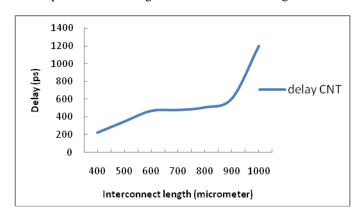

# c. Effect of interconnect length on bundle SWCNT delay

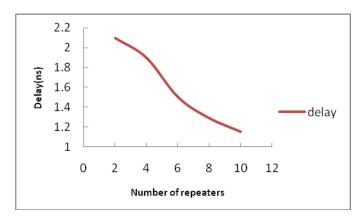

The circuit considered for analysis [2,5-7] comprise a CMOSinverter driving a distributed RLC model of interconnect. A load capacitance of 10fF terminates the interconnect and 0.1Ghz pulse of 1ns rise time provides input to the CMOS inverter. The performance of this setup is studied by SPICE simulation in 32nm technology node with Predictive technology model (PTM)[19] and optimum number of repeaters are used. 90% average delay is illustrated in fig.4 as a function of interconnect length. Result shows that 90% average delay increases with length of interconnect. The variations are simply reflections of the effects of interconnect impedance parameters as shown in figure 3. The increase of normalized delay indicates dominance of CNT resistance over its capacitance. Fig.5 shows the delay as a function of number of repeaters. This result reveals that delay decreases with increase in number of repeaters due to smaller value of RC product in each equal distributed segment of interconnect length.

Figure 4. Variation of 90% average delay of SWCNT bundle as a function of interconnect length.

Figure 5.Variation of 90% average delay of SWCNT bundle as a function of number of repeaters.

## **IV. Conclusion**

An analytical model for the calculation of output voltage of an L segment RLC equivalent circuit is presented. Good agreement between analytical and SPICE simulation results is achieved in saturation region. Applying the concept of L-equivalent distributed circuit to SWCNT bundle interconnect the influence of interconnect length and number of repeaters on propagation delay is also analyzed. The analysis shows that 90% delay of SWCNT- bundle interconnect increases with increase in length of interconnect due to the dominance of interconnect impedance parameters. Whereas opposite is true for the repeaters insertion in long interconnects.

#### References

- W.Steinhogl, G.Schindler, G.Steinlesberger, M.Tranving, and M.Engelhardt, "Comprehensive study of the resistivity of copper wires with lateral dimensions of 100nm and smaller," *Journal of Applied Physics*, Vol.97, 023706, 2005.

- [2] Naeemi et al. "Performance comparison between carbon nanotube and copper interconnects for giga scale integration (GSI)", *Electron Device* letters, vol. 26, No. 2, pp. 84-86, 2005.

- [3] S.Sarkar, M.K.Rai and Nivedita, "Carbon Nanotube Based interconnects for VLSI Application", *IE (1) Journal- ET*, Volume91, January 2011.

- [4] Franz Kreupl et al., "Carbon nanotubes for interconnect applications" Electron Devices Meeting, 2004. IEDM Technical Digest. IEEE International, pp. 683-686, 2004.

- [5] Hong Li et al., "Carbon Nanomaterials for Next- Generation Interconnects and Passives: Physics, Status, and Prospects" IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 56, NO. 9, September 2009.

- [6] Banerjee K. and Srivastava N., "Are Carbon Nanotubes the Future of VLSI Interconnections?" 43rd ACM IEEE DAC Conference Proceedings, San Francisco, CA, pp. 809-14 2006.

- [7] M. K. Rai and S. Sarkar, "Influence of tube diameter on Carbon nanotube interconnect delay and power output", *Physica Satus Solidi A* 298, No.3, pp. 735-739, 2011.

- [8] R. Arunachalam, F. Dartu, L.T. Pileggi, "CMOS gate delay models for general RLC loading", in: Proc. IEEE Int. Conf. Comput. Design: VLSI Comput. Process, pp. 224–229, 1997.

- [9] A. B. Khang and S Muddu, "Accurate Analytical delay models for VLSI interconnects" *UCLA Computer Science Department* TR-950034, Sept. 1995.

- [10] Y. I. Ismail, E. G. Friedman, and J. L. Neves, "Figures of merit to characterize the importance of on- chip inductance," in *Proc. IEEE/ACM Design Automat. Conf.* pp. 560–565, June 1998.

- [11] K Banerjee and A Malhotra, "Analysis of On-chip inductance effect using a novel performance optimization methodology for Distributed RLC Interconnects" *Proceedings of the Design Automation Conference, Las Vegas*, NV, pp. 798–803, 2000.

- [12] K Banerjee and A Malhotra, "Analysis of On-chip inductance effect for Distributed RLC interconnects", IEEE Transaction on Computer Aided-Design of Integrated Circuits and Systems, VOL. 21, NO.8, August 2002.

- [13] J.A. Davis, J.D. Meindl, "Compact distributed RLC interconnect models—Part I: single line transient, time delay and overshoot expressions", *IEEE Trans. Electron Dev.* Vol. 47, pp. 2068–2077, Nov. 2000

- [14] J.A. Davis, J.D. Meindl, "Compact distributed RLC interconnect models—Part II: coupled line transient expressions and peak crosstalk in multilevel interconnect networks", *IEEE Trans. Electron Dev.* Vol. 47, pp. 2078–2087, Nov. 2000.

- [15] R. Venkatesan, J.A. Davis, J.D. Meindl, "Compact distributed RLC interconnect models— Part III: transients in single and coupled lines with capacitive load termination", *IEEE Trans. Electron Dev.* Vol. 50, pp. 1081–1093. April 2003.

- [16] R. Venkatesan, J.A. Davis, J.D. Meindl, "Compact distributed RLC interconnect models— Part IV: unified models for time delay, crosstalk, and repeater insertion", *IEEE Trans. Electron Dev.* Vol. 50, pp. 1094–1102, April 2003.

- [17] T. Sakurai, A.R. Newton, "Alpha-power law MOSFET model and its applications to CMOS inverter delay and other formulas", *IEEE Journal* of Solid-State Circuits, vol. 25, pp. 584–594, April 1990.

- [18] B K Kaushik, Sankar Sarkar, R P Agarwal "Waveform analysis and delay prediction for a CMOS gate driving RLC interconnect load", INTEGRATION the VLSI Journal vol. 40, pp. 394-405, 2007.

- [19] Predictive Technology Model[Online].www.eas.asu.edu/ ptm/.

About Authors:

Devenderpal Singh He received his B-Tech degree in ECE from Lovely Professional University, Jalandhar Punjab, India in 2011. He is currently doing

M-Tech in VLSI Design & Auto CAD from Thapar University, Patiala, India. His research interests include Design of VLSI Interconnects & Digital Electronics.

Mayank Kumar Rai He received the B.E degree from M. J. P. Rohilkhan University, Bareilly, India in 2003 and the M.Tech degree from G. G. S. I. P. University, New Delhi, India in 2007. He is currently

working towards the Ph.D degree in the department of Electronics and communication engineering, Thapar University, Patiala, India. He has over 11 publications in International referred journals, conferences and one book chapter on VLSI interconnects. He is also working as Assistant professor in the department of Electronics and Communication Engineering, Thapar university, Patiala, India. From 2007 to 2009, he was a faculty with FET, MITS, Lakshmangarh, Rajasthan India. His research interest includes the modeling and design of future VLSI interconnects.