Publication Date: 05 June 2013

# Decoupling Capacitor Induced Bandwidth and Delay expressions for On-Chip RLC global interconnects

Santosh Ku Chhotray, Sandeep Ku Dash, Subhakanta Swain, Mrigendra Kumar, Nivedita Rout

Abstract— Continuously scaling down devices is the main goal in deep sub-micron (DSM) technology. Though using DSM technology we are achieving many advantages. But circuit performances are badly affected because of secondary effects like crosstalk noise. According to International Technical Roadmap for Semiconductors(ITRS) 2011 report today's DSM technology outsmarted Moore's law to work in a new industrial trend called "More than Moore" (MtM). To accomplish this, it is necessary to analyze the timing behavior of the interconnect. Decoupling capacitor can have significant effect on principal characteristics of an integrated circuit (IC) i.e. speed, cost and power. So by including a decoupling capacitor intentionally can control secondary effects in very deep sub-micron (VDSM) technology. But inserting a decoupling capacitor affects delay and bandwidth of the interconnect. So while inserting decoupling capacitor we have to check for the disturbances in delay and bandwidth. Here in this paper two expressions for calculating delay and bandwidth have derived.

${\it Keywords} {-\!\!\!\!--} \ {\bf Decoupling \ capacitor, \ interconnects, \ Bandwidth, } \\ {\bf Delay}$

#### **I.** Introduction

An electronic system consists of 2 parts: the basic components (transistor, diode, passive circuit elements, MEMS etc.) and the highly complex interconnect fabric linking them(from local to global in a hierarchical manner). As global interconnects are responsible for power supply, so any disturbance in global interconnect can effect a lot to signal propagation along it and the victim (idle) interconnect. Circuit integration densities rise with each very deep sub-micron (VDSM) due to smaller devices and larger dies. By using VDSM technology we are achieving many advantages. Again to handle high speed and low power in VDSM technology we intentionally add decoupling capacitors to interconnect line. But these decoupling capacitors show some unexpected results because of secondary effects like crosstalk noise. Because of crosstalk functional and timing problems arises like delay, bandwidth etc. Several factors bound to VDSM technology like density of integration, no. of metal layers etc are reason behind these unexpected outcomes. RC modelling is not enough for global interconnection at high frequencies. Working in VDSM technology we cannot ignore wire resistances, capacitances and inductances. So to handle this two-fold nature of VDSM technology here in our proposed model we focus on global interconnects where we consider wire resistances, inductances and practical decoupling capacitances. The timing parameters like propagation delay and bandwidth depends on power supply level during the signal transition. Various techniques have been proposed for the delay analysis of global interconnects. Here in this paper the crosstalk effects because of capacitive coupling and inductive coupling are considered on different nodes of global interconnects. Then using derived expression delay and bandwidths are calculated and compared with 180nm HSpice technology.

## п. Decoupling capacitor effects

Decoupling capacitors are often utilized to manage the power supply noise. Due to importance of decoupling capacitors in current and future ICs, significant research has been developed over past several decades. To be effective, the decoupling capacitor should satisfy two requirements. First, the capacitor should have sufficient capacitance to store a significant amount of energy. Second, to supply sufficient power at high frequency, the capacitor should be able to release and accumulate energy at high rate.

## ш. Proposed Model

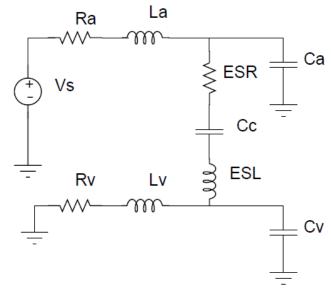

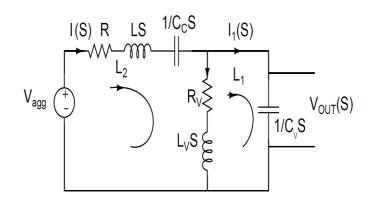

Figure 1 Proposed model with decoupling capacitor

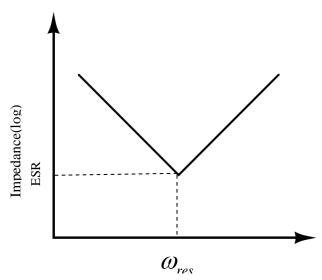

Above figure shows two interconnect lines connected by a decoupling capacitor. At high frequency as the frequency increases, the impedance of the decoupling capacitor increases linearly with frequency as shown in fig. 2. This increase in the impedance of a practical decoupling capacitance is due to the

> Globalize The Research Localize The World

Volume 2 : Issue 2

[ISSN 2319 - 7498]

**Publication Date: 05 June 2013**

parasitic inductance of the decoupling capacitor. The parasitic inductance is referred to as the Effective Series Inductance (ESL) . The impedance of a decoupling capacitor reaches minimum impedance at frequency  $\omega = \sqrt[1]{LC}$  to get negligible disturbance in delay and bandwidth. Effective Series Resistance (ESR) of a decoupling capacitor is the minimum impedance of the decoupling capacitor.

Frequency(log)

Figure 2 Frequency Vs Impedance plot for high frequency interconnect

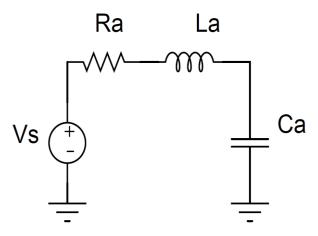

Figure 3 Equivalent model of aggressor line

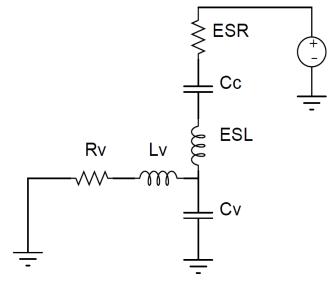

Proposed estimation method separates the victim (idle) net and the aggressor net into two equivalent circuits. The aggressor is modeled as shown in Fig. 3 and victim line is modeled as shown in Fig. 4.

Figure 4 Equivalent model of victim line

Figure 5 Equivalent circuit

#### A. Bandwidth Calculation

$$V_{agg}(t) = \begin{cases} \frac{t}{\tau_a} V_{dd} & 0 < t < \tau_a \\ V_{dd} & t > \tau_a \end{cases}$$

(1)

It can be represented in S-domain as

$$V_{agg}(s) = \frac{1}{s^2 \tau_a} V_{dd} \tag{2}$$

Here for simplicity we have taken  $V_{dd}=1$ .

Proposed model is based on the above circuit shown in Fig. 5. Figure represents victim line parameters and  $V_{\text{out}}(S)$  is the coupled voltage of decoupling capacitor.

#### UACEE International Journal of Advancements in Electronics and Electrical Engineering – IJAEEE Volume 2: Issue 2 [ISSN 2319 - 7498]

Publication Date: 05 June 2013

Now applying KVL to loop L<sub>1</sub>

$$-\frac{I_{1}}{C_{V}S} + L_{V}S(I - I_{1}) + R_{V}(I - I_{1}) = 0$$

$$(\frac{1}{C_{V}S} + L_{V}S + R_{V})I_{1} = I(L_{V}S + R_{V})$$

$$I = \frac{(\frac{1}{C_{V}S} + L_{V}S + R_{V})I_{1}}{(L_{V}S + R_{V})}$$

(3)

$$V_{agg}(S) - RI - LSI - \frac{I}{C_C S} - R_V(I - I_1) - L_V S(I - I_1) = 0$$

$$V_{agg}(S) - I(R + LS + \frac{1}{C_C S} + R_V + L_V S) + (L_V S + R_V)I_1 = 0$$

$$V_{agg}(S) = \frac{(\frac{1}{C_V S} + L_V S + R_V)I_1}{(L_V S + R_V)}(R + LS + \frac{1}{C_C S} + R_V + L_V S) + (L_V S + R_V)I_1$$

$$I_{1}(S) = \frac{V_{agg}C_{C}S(L_{V}C_{V}S^{2} + R_{V}C_{V}S)}{\begin{bmatrix} C_{V}S(L_{V}C_{V}S^{2} + R_{V}C_{V}S + 1)(RC_{C}S + R_{V}C_{C}S + LC_{C}S^{2} + L_{V}C_{C}S^{2}) \\ -(R_{V} + C_{V}S)(L_{V}C_{V}S^{2} + R_{V}C_{V}S)C_{C}S \end{bmatrix}}$$

(4)

$$V_{out}(S) = \frac{I_1}{C_v S} \tag{5}$$

Now using (4) in (5) and rearranging

$$\frac{V_{out}(S)}{V_{agg}(S)} = \frac{C_C S(L_V C_V S^2 + R_V C_V S)}{\begin{bmatrix} C_V S(L_V C_V S^2 + R_V C_V S + 1)(RC_C S + R_V C_C S + LC_C S^2 + L_V C_C S^2) \\ -(R_V + C_V S)(L_V C_V S^2 + R_V C_V S)C_C S \end{bmatrix}}$$

Considering dominating pole and ignoring higher order terms

$$\frac{V_{out}(S)}{V_{oov}(S)} = \frac{jC_C L_V C_V \omega + R_V C_V C_C}{RC_V C_C + R_V C_V C_C}$$

Applying modulus on both sides and equating to  $\frac{1}{\sqrt{2}}$

$$\frac{1}{\sqrt{2}} = \frac{\sqrt{(C_C L_V C_V \omega)^2 + (R_V C_V C_C)^2}}{RC_V C_C + R_V C_V C_C}$$

$$\omega^{2} = \frac{1}{\left(\frac{RC_{V}C_{C} + R_{V}C_{V}C_{C}}{\sqrt{2}C_{C}L_{V}C_{V}}\right)^{2} - \left(\frac{R_{V}C_{V}C_{C}}{C_{C}L_{V}C_{V}}\right)^{2}}$$

$$\omega = \frac{1}{\sqrt{\left(\frac{RC_{V} + R_{V}C_{V}}{\sqrt{2}L_{V}C_{V}}\right)^{2} - \left(\frac{R_{V}}{L_{V}}\right)^{2}}}$$

$$f_{3dB} = \frac{1}{2\pi\sqrt{\left(\frac{RC_{V} + R_{V}C_{V}}{\sqrt{2}L_{V}C_{V}}\right)^{2} - \left(\frac{R_{V}}{L_{V}}\right)^{2}}}$$

(6)

### **B. Delay Calculation**

For calculation of delay we consider 50% rise time when  $V_{out}(t)=0.5V_{dd}$

From (5) we can get delay express

$$V_{agg}(S) = \frac{V_{agg}(S) = \frac{V_{agg}C_{cS} + R_{v} + L_{v}S) + (L_{v}S + R_{v})I_{1}}{(L_{v}S + R_{v})I_{1}}$$

From (5) we can get delay expression as

$$V_{out}(S) = \frac{V_{agg}C_{cS}(L_{v}C_{v}S^{2} + R_{v}C_{v}S)}{\frac{V_{out}(S)}{C_{v}S(L_{v}C_{v}S^{2} + R_{v}C_{v}S + L)(RC_{c}S + R_{v}C_{c}S + LC_{c}S^{2} + L_{v}C_{c}S^{2})}}{\frac{V_{out}(S)}{C_{v}S(L_{v}C_{v}S^{2} + R_{v}C_{v}S + LC_{c}S^{2} + L_{v}C_{c}S^{2})}}{\frac{V_{out}(S)}{C_{v}S(L_{v}C_{v}S^{2} + R_{v}C_{v}S + LC_{c}S^{2} + L_{v}C_{c}S^{2})}}}$$

Now for delay calculation equating  $V_{out}(t) = 0.5V_{dd}$

Now for delay calculation equating  $V_{out}(t)=0.5V_{dd}$

$$V_{out}(S) = \frac{0.5V_{dd}}{S}$$

Using above value in (7)

$$\frac{0.5V_{dd}}{S} = \frac{\frac{V_{dd}}{s^2 \tau_a} C_C S(L_V C_V S^2 + R_V C_V S)}{\begin{bmatrix} C_V S(L_V C_V S^2 + R_V C_C S + L)(RC_C S + R_V C_C S + LC_C S^2 + L_V C_C S^2) \\ -(R_V + C_V S)(L_V C_V S^2 + R_V C_V S)C_C S \end{bmatrix}}$$

Now taking inverse Laplace transform and solving

$$t_{50\%} = 1.18 * \sqrt{3X^2 - 2Y}$$

$$X = R(C_V + C_C) + R_V C_V - \frac{R_V}{L_V}$$

$$Y = RR_{V}C_{V}C_{C} + \frac{R_{V}^{2}C_{C}}{L_{V}} - \frac{R^{2}C_{V}}{L_{V}}$$

## **IV.** Simulation Result and **Discussion**

Our experimented high-speed interconnect system consist of two coupled interconnect lines of length d=100 um. The extracted values for the parameters R, L, and C are given in Table 1.

Table I RLC Parameters for a Minimum- Sized Wires in a 0.18µm Technology

| 10011110108)             |            |  |  |  |

|--------------------------|------------|--|--|--|

| Parameter(s)             | Value/m    |  |  |  |

| Resistance(R)            | 120 kΩ/m   |  |  |  |

| Inductance(L)            | 270 nH/m   |  |  |  |

| Coupling Capacitance(Cc) | 681.23pF/m |  |  |  |

| Capacitance(C)           | 240 pF/m   |  |  |  |

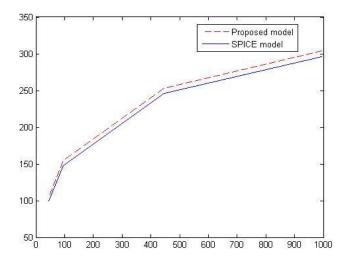

Table-II compares the bandwidth we got by proposed model with the values from SPICE simulator for different source resistances. With the varying source resistance we got different values of bandwidth with approximately 3.881% of error.

Table II Bandwidth comparison of proposed model with SPICE model

| $R_s(\Omega)$ | L <sub>s</sub> (pH) | $C_c(pF)$ | SPICE     | Proposed | %      |

|---------------|---------------------|-----------|-----------|----------|--------|

|               | _                   | _         | Bandwidth | Model    | Error  |

|               |                     |           | (MHz)     | (MHz)    |        |

| 45            | 2.5                 | 0.175     | 99.74     | 105.13   | 5.4040 |

| 95            | 2.5                 | 0.175     | 147.64    | 154.43   | 4.5990 |

| 445           | 2.5                 | 0.175     | 245.72    | 252.71   | 2.8447 |

| 995           | 2.5                 | 0.175     | 295.9     | 303.82   | 2.6765 |

Figure 6 Bandwidth comparison of proposed model with SPICE model

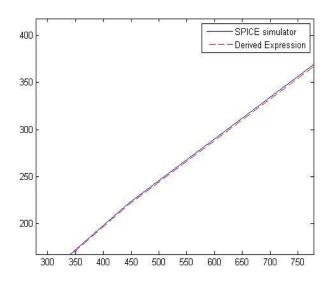

Fig.5 shows the deviation of bandwidth using derived expression from SPICE simulator and Fig. 7 shows the deviation of delay using derived expression from SPICE simulator

Table-III compares the delay we got using derived expression with SPICE simulator values and the average percentage of error is about 0.5499%.

Table III Delay comparison of Proposed model with SPICE model

| D             | Delay comparison of Froposed model with SFICE model |           |           |           |        |  |  |  |

|---------------|-----------------------------------------------------|-----------|-----------|-----------|--------|--|--|--|

| $R_s(\Omega)$ | $L_s(pH)$                                           | $C_c(pF)$ | SPICE     | Proposed  | %      |  |  |  |

|               |                                                     |           | Delay(ps) | Model(ps) | Error  |  |  |  |

| 45            | 2.5                                                 | 0.175     | 20.14     | 20.05     | 0.4468 |  |  |  |

| 95            | 2.5                                                 | 0.175     | 41.55     | 41.35     | 0.4813 |  |  |  |

| 445           | 2.5                                                 | 0.175     | 221.36    | 220.03    | 0.6008 |  |  |  |

| 995           | 2.5                                                 | 0.175     | 465.13    | 462.01    | 0.6707 |  |  |  |

Figure 7 Delay comparison of proposed model with SPICE model

#### Conclusion

In this study simple and explicit analytical expressions have been proposed for calculating delay and bandwidth for global interconnects in very deep sub-micron (VDSM) technology where we consider decoupling capacitors for controlling signal timing behavior. It is expected that these expressions will also applicable to 90nm and 45nm technology and to be used efficiently in high speed and large scale circuits. Hence these closed form expressions can be implemented in VLSI design tool for efficient modeling of interconnection in high speed VLSI chips. These analytical delay formulas are much faster than simulating using SPICE. So can save time and of course the cost of using expensive tools like SPICE. In future we will try to simplify these equations to simpler form as possible.

**Publication Date: 05 June 2013**

#### **Acknowledgment**

The authors would like to thank Dr Rajib Kar for all his assistance. Samir ku jha, M.Panda, D.Agarwal, D.kannoujia, V.Kumar and R.S.S.M.R. Krishna are also acknowledged for their support.

#### References

- [1] R. Venkatesan, J. Davis, and J. Meindl, "Compact distributed RLC interconnect models ---part IV: unified models for time delay, crosstalk, and repeater insertion," IEEE trans. Electron Devices, vol.50, no. 4, April, 2003, pp.1094-1102.

- [2] S. K. Chhotray, V. Maheshwari, A. Bansal, R. Kar, D. Mandal, A. K. Bhattacharjee, "Crosstalk aware Bandwidth Modelling for VLSI RC Global Interconnects using 2-π Model", Procedia Technology Journal, vol. 6, pp. 832 – 839, 2012, Elsevier.

- [3] Santosh Ku Chhotray, Deepak Agarwal, Subhakanta Swain, Dheeraj Kannoujia, Vinod Kumar, "An analytical Bandwidth and Delay expression for RLC global interconnects", ICMARS'12.

- [4] Mingcui Zhou, Wentai Liu, Mohanasankar Sivaprakasam "A Closed-form Delay Formula for On-Chip RLC Interconnects in Current-Mode Signaling" Department of Electrical Engineering, University of California at Santa Cruz, CA 95064, USA ©2005 IEEE.

- [5] Kahng and S. Muddu, "Efficient Gate Delay Modeling for Large Interconnect Loads," IEEE Multi-Chip Module Conf., Feb. 1996.

- [6] Y.I. Ismail, E.G. Friedman, "Equivalent Elmore delay for RLC trees," IEEE Trans, computer-aided design, vol.19, no 1, Jan

- [7] W. C. Elmore, "The transient response of damped liner network with particular regard to wide band amplifier," J. Appl. Phys, vol.19, pp55-63, 1948.

- [8] S. Y. Kim, K. Y. Kim and S. Y. Kim, "The Algebraic Calculation of the Delay Time using the Reduction Model of RCclass Interconnect," KIEE Trans, vol 52C, no 5, pp193-200

About Author (s):

Santosh Kumar Chhotray received B.Tech from BPUT, Orissa and continuing M.Tech in the specialization of Microelectronics and VLSI in National Insti. Of Technology, Durgapur, West Bengal, India.

For last 1 year he has performed research in the areas of IC interconnect characterization, modeling and simulation for the high speed and low power application. His research interests are high speed and low power SRAM design, interconnect modeling.

Sandeep Kumar Dash received B.Tech from BPUT, Orissa in 2010. And continuing his M.Tech in the specialization of Microelectronics and VLSI in National Insti. Of Technology, Durgapur, WestBengal,India.. He has performed research in the areas of ideal Op-Amp characterization for the high speed application. His research interests are filter design, Mixed signal IC design for low power application.

Subhakanta Swain received B.Tech from BPUT, Orissa in 2010. And continuing his M.Tech in Sikhsa 'O' Anushandhan University, Bhubaneswar, Orissa, India. He has performed research in the areas of Wireless multimedia sensor networks. His core area of research is Priority-based rate control for service differentiation and congestion control in Wireless multimedia sensor networks.

Mrigendra Kumar received B.Tech from WBUT, Kolkata in 2012. He is doing research in VLSI system modeling. His area of interests are control system, signal processing and VLSI interconnections.

Nivedita Rout received B.Tech from BPUT, Orissa in 2012. She is working as teaching assistant in Aryan Insti. Of Technology and working on power issues related to VLSI circuits. Her core area of research are Automated access of information and fast data tracking.