# To study and analyse Mixers under CMOS Technology

Shilpa Mehta, Mrs Vandana Khanna

**ITM University**

### shilpa.frnd1155@gmail.com

# Abstract

In this paper various mixers are defined for CDMA applications . Using CMOS makes easier for mixers to act on same chip with other digital and analog circuits . The topologies we are defining are dual gate mixers , back gate mixers, single balanced current switching mixers and back end mixers . The backgate mixer utilizes the inherent lateral bipolar transistor in CMOS. Device simulations were performed to analyze the behavior of the lateral bipolar transistor and extract a madel for it. The characteristic of the transistor were verified through measurements. The mixer circuit only draws 1.3 mW from a 1 V supply . Other mixers are also defined not only to achieve linearity , but also conversion gain and power dissipation.

## Introduction

The back-gate mixer utilizes the inherent lateral bipolar transistor in CMOS. Device simulations were performed to analyze the behavior of the lateral bipolar transistor and extract a madel for it. The characteristic of the transistor were verified through measurements. The mixer circuit only draws 1.3 mW from a 1 V supply

| Configuration<br>of Mixer    | Conversion<br>Gain (dB) |      | Input 1 dB<br>Compression<br>Point (dBm) |       | Noise<br>Figure<br>(dB) | Mixer<br>Current<br>(mA) |

|------------------------------|-------------------------|------|------------------------------------------|-------|-------------------------|--------------------------|

|                              | Sim                     | Meas | Sim                                      | Meas  | Sim                     | Meas                     |

| Single Bal-<br>anced CS      | 3.8                     | 2.4  | -9                                       | -11.3 | 15.62                   | 1.32                     |

| Single Bal-<br>anced Cascode | 4.5                     | 4.7  | -3.9                                     | -14.6 | 14.5                    | 1.43                     |

| Double Bal-<br>anced CS      | 8.1                     | 6.1  | -5.2                                     | -8.3  | 8.33                    | 2.24                     |

| Double Bal-<br>anced Cascode | 6.7                     | 6.9  | -5.9                                     | -13.3 | 10.04                   | 2.18                     |

| Single Cas-<br>code          | 8                       | 4.8  | -12.2                                    | -20.8 | 10                      | 6.11                     |

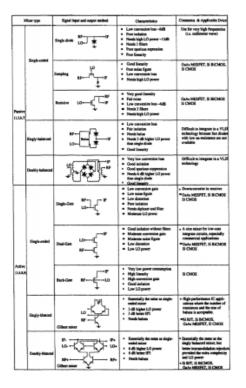

Silicon MOSFET dual-gate mixers have been widely used in mobile and hand-held radio transceivers since the 1960s [II. They exhibit good noise figures and reasonable conversion gains and most importantly, they allow the application of the two input signals to two separate gates thus making separate LO and RF matching possible thus avoiding passive couplers and simplifying the design. The inherent isolation between the gates of the two FETs also results in very good LO-to-RF isolation without the use of filters. A double balanced CMOS dual-gate mixer has ken reported [4]. However, low voltage single ended dual-gate CMOS mixers have not been reported thus far. The absence of a theoretical distortion analysis makes it difficult to predict and optimize the intermodulation performance of such a mixer.

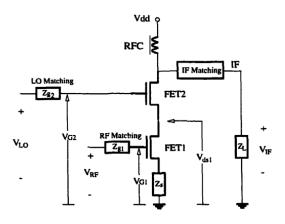

Fig 1.1 Dual Gate Mixer

Two MoSFETs (FETI and FET2) are connected in a cascode configuration. The LO signal Vto is injected into the gate of FET2 while the RF signal VRF is injected into FET1. The IF output signal Vw is accessed from the drain of FET2. Zgl and Zg2 represent for the input matching networks associated with FET1 and FET2 respectively. Z, is the source impedance associated with the source of FET1. "IF Matching" is the output matching network, and ZL is the load usually 50 Q RFC is the RF choke used to prevent the RF signal from flowing through the power supply Vdd to ground. VG1 and VG2 are bias voltages applied to the gates of FET 1 and FET;! respectively. The SOI devices have zero threshold voltages and the supply voltage chosen is 1 V.

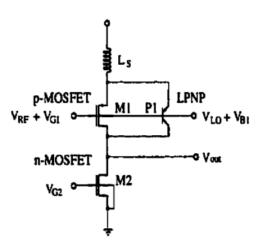

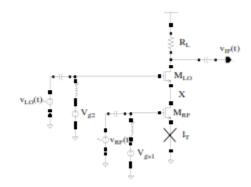

Fig 1.2 Back Gate Mixer

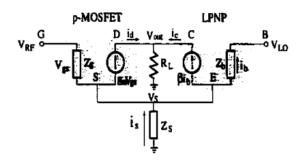

Fig 1.3 Back Gate Equivalent

A pMOSFET M 1 with an inherent LPNP P 1 is usd as a four terminai device. The RF input signai Vw is applied to the gate of the MOSFET and the LO signal VLO is fed to the substrate or base of the LPNP. The 11: output signai V,,, is accessed from the drain. VG VB1 and Vdd are the bias and supply voltages respectively. The n-MOSFET M2 acts as a load and the conversion gain of the mixer can be adjusted by changing its gate voltage VG2. LS is used to shift the ac voltage level at the source of M Vp, is the signal voltage across Zg which is the impedance associated with the gate of Ml, g, is the transconductance of Ml, Zs is the impedance of Ls, is the current gain of Pl and & is the impedance associate with the base of the LPNP. To simplify the circuit, the n-MOSFET is replaced by a resistor RL. VS is the voltage at the source of the Ml.

#### **1.3 Single Balanced Current-Switching Mixers**

Mixers based on the multiplication of two signals exhibit superior performance as they ideally generate only the desired mixing products. Both the RF and LO signals are applied at different ports resulting in high degree of inherent isolation among all the three ports. Down-conversion mixers usually employ LO short at the IF port to achieve optimum IM performance. The LO short is practically important for the active mixers because LO signal is typically larger than the RF signal and it is further amplified by the active devices. The mixer that accommodates a differential LO signal and a single-ended RF signal is termed as single-balanced mixer.

Fig 1.4 Single balanced Current Switching Mixers

In Figure the incoming RF voltage signal is first converted into a current signal and then multiplied in current domain. The FETs ,MLO1 and Mv RF(t) are biased slightly above their threshold level. This results in the LO alternatively switching MLO2, LO1and M on

and off. Consequently, one LO transistor is always on, while other LO transistor is ideally off, keeping the RF transistor in saturation. Hence, the LO signal can be considered as a square wave consisting of odd harmonics of the LO frequency. The magnitude of this signal should be large enough to ensure complete switching of the differential LO transistors. The RF input current signal is multiplied by the odd-order harmonics of LO signal, resulting in mixingproducts to appear at the output IF port.

#### 1.4 Single Cascade Mixer

Figure shows a simple CMOS single-cascode mixer. The upper transistor has several effects on the mixer operation. Its primary use is to control the small signal transconductance of the lower device and therefore, the RF gain of the device, making it useful as a mixer [6]. In addition, this configuration is well suited to CMOS technology since the drain and source of the two cascoded devices can be shared reducing capacitance at the common junction. It has been proved that the usual mode of operation is the one in which LO signal is applied to the top gate and theRF signal is fed to the lower gate [6-7]. This not only improves the LO ,RF-to-IF isolation but also enhances the linearity by allowing the use of standard port matching techniques for the RF signal. The applied LO signal modulates the common node voltage . The modulated node is the drain of M resulting in the mixing of LO and RF signal. The gate-source voltage of M RF is approximately constant because the RF signal is usually very small and the modulated drain-source voltage swings Min and out of linear and saturated regions of operation over the LO cycle. Fre- quency mixing occurs due to the modulated transconductance g and drain-source conductance g ds of M R.M remains in current saturation over most of the LO cycle, thus, it operates, simultaneously, as a source-follower amplifier for the LO and a common RF.

#### Conclusion

All these mixers are studied and defined to obtain better results in order to attain linearity, Conversion gain, slew rate, power dissipation and frequency.

#### References

Q. Huang, P. Orsatti and F. Piazza, "GSM Transceiver Front-End Circuits in 0.25-um CMOS,"iEEE Journal of Solid-State Circuits, Vol. 34, No. 3, pp 292-303, 1999.

[2] T.W. Pan and A. A. Abidi, "A 50dB Variable Gain Amplifier Using Parasitic Bipolar Transistors in CMOS," IEEE Journal of Solid-State Cinuirs, Vol. 24, No. 4, pp 951-961,1989.

[3] Yan, M. J. Deen and D. S. Malbi, 'Qate-ControUed Lateral PNP BJT Characteris-tics, Modeling and Circuit Applications," IEEE Tmmactions on Elecmn Devices, Vol. 44, pp. 118-128,1997, [4]J. R. Long and M. A. CopeIand, 'The Modeling, Characterization, and Design of Monolithic inductors for Silicon RF IC's," IEEE Journal of Solid-Sîate Circuits, V01.32,pp. 357-369, 1997. [SIA. Valkodai and T. Manku, "Modeling and designing silicon thinfilm inductors and transfomers using HSPICE for RFIC applications," htegration, the YLSIjoumal, Vol 24,pp. 159-171,1997.

[6] H. Ronkainen, H. Kattelus and E. Tarvainen, 'SC compatible planar inductors on di-con," IEE Proc. Circuits Devices Sysrem, Vol 144, pp. 29-35, 1997

[7] S. A. Maas, The RF and Microwave Circuit Design Cookbook, Artech House, Boston, MA, c1998.

[8] A. M. Pavio and R. H. Halladay, "A Distributed Double-Balanced Dual-Gate FET Mixer," IEEE GaAs IC Symposium, pp. 177-180, 1988.

[9] J. Fikart and P. Acimovic, "Single-Ended Mixer with Reduced LO Penetration," IEEE Pac@c Rim Conference on Communications, Computers and Signal Processing, pp.63-66, 1991.

[10] P. J. Sullivan, B.A. Xavier and W.H. Ku, "Double bdanced dual gate CMOS mixer,"IEEE Journal of Solid-State Circuits, Vol. 34, pp. 878-88 1, 1999.

[11]j D. A. Johns and K. Martin, Andog Integrated Circuit Design, John Wiley & Sons Inc., c 1997.

[12] W. Yu, S. Sen and B. H. Leung, "Distortion Analysis of MOS Track-and-Hold Sam- pling Mixers Using Time-Varying Volterra Series," IEEE Transactions on Circuits and Systems- II: Analog and Digital Signal Pmcessing, Vol. 46, pp. 101-1 13, 1999.