# A Low-Power Circuit Technique for Dynamic CMOS Logic

Preetisudha Meher Dept. of Electronics and Telecommunication National Institute of Technology Rourkela, India Preetisudha1@gmail.com

Abstract-- Dynamic logic style is used in high performance circuit designs because of its faster speed and lesser transistor requirement as compared to static CMOS logic style. Dynamic logic has inherent disadvantages like less noise immunity and high power consumption. In this paper we have proposed a novel circuit technique for implementing dynamic gate. The proposed circuit has very less power dissipation with almost same noise immunity compared to the recently proposed circuit techniques for dynamic logic styles to improve noise immunity. The concept is validated through extensive simulation.

*Keywords--* Domino logic, dynamic logic, power consumption, leakage tolerance, robustness.

### I. INTRODUCTION

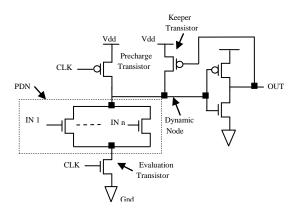

Dynamic logic is used in the implementation of logic circuit for high speed designs such as data path in microprocessor [1]. However, it is not widely used because of its disadvantages like less noise robust and more power consuming compared to static logic style [2]. Domino logic is made by adding one inverter at the output of the dynamic gate. Domino gate has got advantage over the dynamic gate because fan-out of former is driven by inverter which has low output impedance and thus increases the noise immunity of the gate along with decreasing the output capacitance [3]. Figure 1 shows the standard domino logic style. Keeper transistor is used to maintain the logic one in the evaluation phase (CLK goes high) when there is charge leakage from the dynamic node through the pull down network (PDN). When PDN is ON in the evaluation phase dynamic node is discharged to zero through the PDN and evaluation transistor. Output inverter starts switching from zero to one and the keeper transistor starts turning OFF from ON. During this period there is static power dissipation from Vdd to Gnd.

During the evaluation phase small noise-signal at the input(s) of dynamic gate can change the desired output because of discharge of dynamic node. In worst case the circuit becomes very less noise-tolerant in case of high-fan in OR gate implementations.

Kamala Kanta Mahapatra Dept. of Electronics and Telecommunication National Institute of Technology Rourkela, India kmaha@gmail.com

Figure1: Standard Domino OR gate.

Noise robustness can be improved by upsizing the keeper transistor (making wider) which makes keeper (PMOS) more conducting and thus maintains the charge at the dynamic node [4]. But this comes at the cost of static power dissipation which flows from Vdd to Gnd through keeper transistor when noise signal arrives at one of the inputs. To make dynamic circuit more noise robust different circuit styles have been proposed [4-9].

In this paper we have presented a novel circuit scheme for the domino logic. When compared with the recent proposals, the proposed circuit scheme has better noise-tolerance and very less power consumption.

The rest of the sections are organized as follows. Some related works for noise robustness in domino logic are described in section II. Section III presents the novel domino circuit approach and simulation results and comparisons are discussed in section IV. Conclusions are presented in Section V.

### **II. RELATED WORKS**

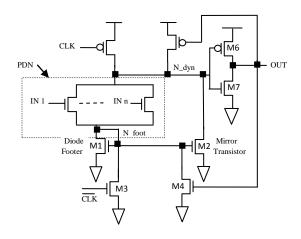

Figure 2 shows the circuit technique proposed in [4] to improve the noise-tolerance. This technique increases the leakage immunity by a footer transistor in a diode configuration and improves the performance by employing a current mirror technique in the evaluation network. The diode footer transistor has voltage drop across it because of leakage in evaluation phase. This voltage drop makes the gate-to-source voltage of the OFF evaluation transistor negative causing the exponential reduction of subthreshold leakage current. But this comes at the cost of performance degradation. This performance degradation is balanced by using mirror transistor. This mirror transistor mirrors the evaluation current and hence improves the performance by the draining current from the dynamic node.

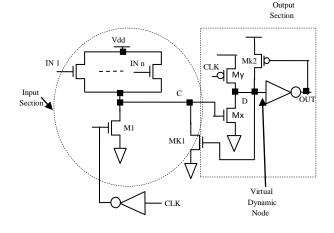

Domino circuit to improve noise tolerance proposed in [5] is shown in Figure 3. At the beginning of the evaluation phase node C is at 0 V. Noise glitches at the input temporarily increases the gate-to-source voltage of the corresponding NMOS in PDN. Increase in the subthreshold current increases the charging of node C. During this process, gate-to-source voltage of the active NMOS decreases and the subthreshold leakage current is exponentially reduced.

Figure 2: Diode footed domino [4]

Figure 3: Domino style proposed in [5]

### III. PROPOSED DOMINO CIRCUIT SCHEME

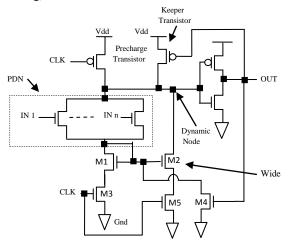

The proposed novel domino circuit scheme is shown in Figure 4. Transistor M1 is used as diode. Due to voltage drop across M1, gate-to-source voltage of the NMOS transistor in the PDN decreases (stacking effect [10]). The proposed circuit differs from [4] as it has additional evaluation transistor M5 with gate connected to the CLK. In [4], when M1 has voltage drop due to presence of noise-signals, M2 starts leaking that causes the circuit to dissipate power and also makes it less noise robust. The purpose of M5 in proposed scheme causes the stacking effect and makes gate-to-source voltage of M2 smaller (M2 less conducting).

Figure 4: Proposed domino circuit scheme

Hence circuit becomes more noise robust and less leakage power consuming. But for performance degrades because of stacking effect in mirror current path. This can be increased by widening the M2 (high W/L) to make it more conducting.

## IV. SIMULATION RESULTS, COMPARISONS AND DISCUSSIONS

Circuits are simulated using HSPICE simulator at temperature of 25 degree Celsius with PTM model card BSIM4 in 45 nm technology for bulk CMOS [11]. Channel length and width taken for simulations are 0.05 um and 0.06 um. Supply voltage Vdd used is 1.8 V. For the noise-tolerance measurement, noise immunity metric, unity noise gain (UNG) is used [4, 5]. Noise pulse width 125 ps (higher than gate delays) are taken and noise-voltages are applied to all inputs. TABLE I shows the UNG normalized to Vdd=1V and power-delay product (PDP) for different schemes of OR gate with fan-in of 2.

Transistor M2 plays a crucial role in terms of leakage and performance of gate in the proposed scheme. Its high width improves the performance but penalty paid is less noise robustness and slightly more power consumption. Vol:1 Issue:1 ISSN 2278 - 215X

| Scheme                                       | UNG (mV) | Power (uW) | Delay (Sec) | PDP        |  |  |  |

|----------------------------------------------|----------|------------|-------------|------------|--|--|--|

| Diode footed domino proposed in [4]          | 478      | 38.1       | 2.72E-11    | 1.036 E-15 |  |  |  |

| Domino proposed in [5]                       | 812      | 81.2       | 4.18E-11    | 3.394 E-15 |  |  |  |

| Proposed domino (W/L = 0.12um/0.05um for M2) | 772      | 7.4        | 4.72E-11    | 3.492 E-16 |  |  |  |

TABLE 1: UNG of Different Styles for 2 INPUTS OR Gate with Vdd Normalized to 1.0 Volt

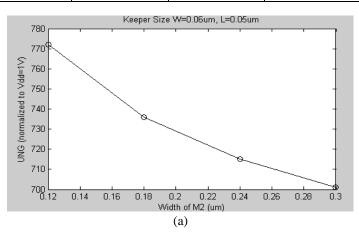

TABLE 2 shows the UNG, power and delay measurements for various widths of M2. With the increased size of keeper transistor there is very high increase in UNG at slightly more power consumption but high increase in delay as shown in TABLE 3.

Figure 5. PDP Comparison of proposed circuit with other circuits

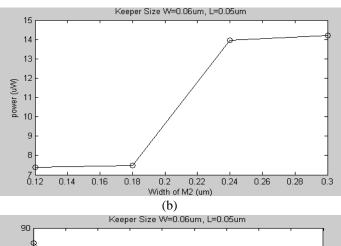

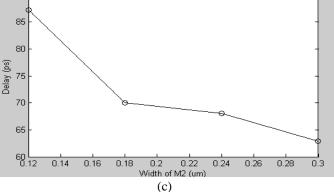

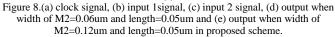

Also, there is increase in UNG as fan-in increases as shown in figure 7. Figure 8 shows the output waveforms obtained in implementation of 2 input OR gate using proposed scheme. It is evident that when width of M2 is less (W/L=1) there is no proper conduction from the dynamic node to ground to discharge the dynamic node. When width of M2 increases (W/L=1.5), proper conduction path is established to discharge the dynamic node and full swing output is obtained.

TABLE 2: UNG and Performance Measurements for Different Width of M2 in

| Width of M2 | UNG (normalized<br>to Vdd=1V) | Power (uW) | Delay<br>(ps) |

|-------------|-------------------------------|------------|---------------|

| 0.12 um     | 772                           | 7.4        | 87.2          |

| 0.18 um     | 736                           | 7.49       | 68            |

| 0.24 um     | 715                           | 13.95      | 68            |

| 0.30 um     | 701                           | 14.2       | 62.9          |

TABLE 3: UNG, POWER and Delay Measured at Different Keeper Transistor Width in Proposed Scheme With Width of M2=0.18um

| Width of Keeper<br>transistor | UNG (normalized<br>to Vdd=1V) | Power (uW) | Delay<br>(ps) |

|-------------------------------|-------------------------------|------------|---------------|

| 0.06 um                       | 736                           | 7.49       | 68            |

| 0.07 um                       | 791                           | 7.72       | 115           |

Figure 6. (a) UNG (normalized to Vdd=1V) ,(b) power and (c) delay for various values of M2 width.

Vol:1 Issue:1 ISSN 2278 - 215X

### 5. CONCLUSION

A novel circuit scheme for the domino logic is proposed. The proposed circuit style is simulated using HSPICE simulator using 45 nm PTM for bulk CMOS model card. Proposed scheme when compared with the recent proposals shows high power savings as well as less power-delay product with almost same noise immunity. Furthermore, UNG increases as fan-in increases. The proposed circuit can be used in design of highspeed embedded processors where low power consumption is an essential requirement.

### ACKNOWLEDGMENT

The authors acknowledge to DIT (Ministry of Information & Communication Technology) for the financial support for carrying out this research work.

### REFERENCES

- F. Frustaci M. Lanuzza P. Zicari S. Perri and P. Corsonello, "Low-power split-path data-driven dynamic logic," *IET Circuits Devices Syst.*, Vol. 3, Iss. 6, pp. 303–312, 2009.

- [2] Rakesh Gnana David J and Navakanta Bhat, "A Low Power, Process Invariant Keeper for High Speed Dynamic Logic Circuits," *IEEE International Symposium on Circuits and Systems, ISCAS*, pp.1668, May 2008.

- [3] J. Rabaey et al., Digital Integrated Circuits, 2nd Edition, Prentice Hall.

- [4] H.Mahmoodi-meimand and K. Roy, "Diode-footed domino: a leakagetolerant high fan-in dynamic circuit design style," *IEEE Trans. Very Large Scale Integr. Syst.*, 51, (3), pp.495–503, 2004.

- [5] F. Frustaci P. Corsonello S. Perri and G. Cocorullo, "High-performance noise-tolerant circuit techniques for CMOS dynamic logic," *IET Circuit Devices Syst.*, vol. 2, No. 6, pp. 537-548, 2008.

- [6] F. Mendoza-Hernandez, M. Linares-Aranda and V. Champac, "Noise tolerant improvement in dynamic CMOS logic circuit," *IEEE Proc.-Circuits Devices Systems*, Vol 153, No. 6, pp. 565-573, Dec 2006.

- [7] O.Gonzalez-Diaz, M. Linares-Aranda and F. Mendoza-Hernaindez, "A Comparison Between Noise-Immunity Design Techniques for Dynamic Logic Gates," 49th IEEE International Midwest Symposium on Circuits and Systems, MWSCAS '06, pp. 484 – 488, 2006.

- [8] Fang Tang, Ke Zhu, Quan Gan and Jian Guo Tang, "Low-noise and power dynamic logic circuit design based on semi-dynamic logic," 2nd International Conference on Anti-counterfeiting, Security and Identification, ASID 2008. 20-23 Aug. 2008.

- [9] Atila Alvaizdpoul, Per Lurssoia-Edefors and Christer Sveizsson, "A Leakage-Tolerant Multi-Phase Keeper For Wide Domino Circuits," *Proceedings of ICECS '99. The 6th IEEE International Conference on Electronics, Circuits and Systems*, pp.209, 1999.

- [10] Kiat-Seng Yeo, Kaushik Roy, "Low-voltage low-power voltage subsystems" Tata Mc-Graw-Hill edition 2009.

- [11] http://ptm.asu.edu/modelcard/2006/45nm\_bulk.pm

- [12] R. J.-H. Sung, D. G. Elliott, "Clock-Logic Domino Circuits for High-Speed and Energy-Efficient Microprocessor Pipelines," IEEE Transactions on Circuits and Systems II: Express Briefs, Vol.54(5), pp.460, May 2007.

- [13] V. Sharma, W.K. Al-Assadi, "Analysis and Modeling of Crosstalk Noise in Domino CMOS Circuits," *IEEE Region 5 Technical Conference*, pp.374, April 2007.

- [14] Song Jia, Fei Liu, Jun Gao, Ling Liu, Xinan Wang, Tianyi Zhang, Zhongjian Chen, Lijiu Ji, "A 64-bit lookahead carry chain in Inverted-Domino logic," *IEEE Conference on Electron Devices and Solid-State Circuits*, pp.281, Dec. 2003.