Vol:1 Issue:1 ISSN 2278 - 215X

# A 0.1-8 GHz Low Noise Amplifier Design Using 0.18 μm CMOS Technology

Jigar Chaudhari, Rachna Jani V.T. Patel Dept. of Electronics and Communication Charotar Institute of Technology, Charusat University Changa, India

jigarchaudhari@yahoo.com, rachnajani.ec@ecchanga.ac.in

Abstract—A T-coil network can be implemented as a high order filter for bandwidth extension. This technique is incorporated into the design of the input matching and output peaking networks of a low-noise amplifier. The intrinsic capacitances within the transistors are exploited as a part of the wideband structure to extend the bandwidth. Using the proposed topology, a wideband low-noise amplifier with a bandwidth of 0.1–8 GHz, a maximum gain of 18 dB and noise figure of 6 dB (min) is achieved. The total power consumption of the wideband low-noise amplifier from the 1.8Vpower supply is 4.5 mW. For design of this type of wideband low-noise amplifier 0.18 µm CMOS technology is used.

Keywords— T-coil network, feedback, bandwidth extension, gain-flatness, center-tap inductor, wideband low-noise amplifier (LNA).

#### I. INTRODUCTION

ULTRA-WIDEBAND (UWB) radio, potentially offers higher communication speeds than traditional narrowband transceivers. The advantage of the UWB transceiver over narrowband systems is low cost, low power, and high data rate due to the large bandwidth. A significant difference between traditional radio transmission and UWB radio transmission is that traditional communications systems transmit data by varying the power level, frequency, and/or phase of a sinusoidal wave. However, in UWB radio, data is transmitted either as impulse radio (IR) or multiband orthogonal frequency division multiplex (OFDM). The IR UWB transmits data based on the transmission of very short pulses.

One of the major challenges in wideband communications systems is the design of a wideband low-noise amplifier (LNA). As the first active component in the receiver chain, the LNA should offer sufficient gain and low noise to keep the overall receiver noise figure as low as possible. In most applications, it is desirable to obtain wideband on-chip input matching to a  $50\Omega$  antenna/filter, good linearity, and low power consumption. In addition, gain-flatness over the entire  $swajan_2004@yahoo.com$

Shruti Oza Electronics and Communication Department Kalol Institute of Technology and Research Centre Kalol, India

frequency range of interest is necessary to meet the design specifications. Recently, many wideband LNA designs in CMOS technology has been reported [1]–[4]. The wideband LNA designs can be classified as multi-band LNAs, distributed amplifiers (DA), and broadband noise canceling LNAs. Among wideband LNA designs, distributed and common-gate amplifiers suffer from high noise figure. Alternatively, the feedback amplifier topology provides wide bandwidth while reducing the gain of the circuit.

The cost and integration advantages of CMOS technology have motivated extensive studies in the high speed CMOS design for wireless applications. Recently, many wideband LNA designs in CMOS technology have been reported [1]–[4]. The wideband LNA designs can be classified as multi-band LNAs, distributed amplifiers (DA), and broadband noise canceling LNAs. Among wideband LNA designs, distributed and common-gate amplifiers suffer from high noise figure. Alternatively, the feedback amplifier topology provides wide bandwidth while reducing the gain of the circuit. Another important property of the negative feedback is the suppression of the nonlinearity. However, in feedback circuits the stability may suffer if the loop gain is too high which the phase margin reaches  $-180^{\circ}$  or the phase margin is so much that the feedback becomes positive. Therefore, compensation techniques are required to eliminate the instability problem. In the noise canceling technique reported in [3], 5 inductors are used and the noise figure is 4.5-5.1 dB from 1.2-11.9 GHz with 20 mW power consumption, which makes it unattractive for low cost, low power applications. In [2], several narrowband amplifiers with different resonance frequencies are cascaded. Therefore, the resulting multistage amplifier provides a broadband response. This circuit required 8 inductors in a differential architecture and since many stages are cascaded it is prone to poor linearity and stability problems.

This paper introduces a T-coil network to achieve wideband input matching and wideband output response. In this technique the parasitic capacitors of the transistors and inherent

mutual inductance of the inductors are taken as a part of the design [4]. In this work 3 inductors are used which 2 of inductors are center-tap inductor. Section II will cover the basic concepts of inductive peaking circuits. In Section III, the T-coil network technique is utilized in a cascode amplifier to realize the wideband LNA for the UWB/multiband applications. In Section IV experimental results of wideband LNA design are shown.

# II. CIRCUIT DESIGN: THEORY AND PRACTICE

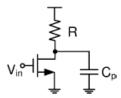

Figure .1 Common-source amplifier with output parasitic capacitance Cp.

In [5], a Chebyshev type band pass filter is used at the input of a common-source amplifier in order to provide good matching over a wide bandwidth.

In general, when the LNA circuit is cascaded to the next stage, the interstage parasitic reactance attenuates the desired bandwidth of the LNA. For example, in Fig. 1 parasitic gate-source capacitance  $C_p$  of a mixer or buffer reduces the circuit performances as it shunts with the output load R of the common source amplifier. A dominant pole due to the parasitic  $C_p$  is created at frequency of  $1/RC_p$  which reduces the bandwidth. One way to compensate  $C_p$  is to insert an inductor in series with R at the output of Fig. 1 to resonate out  $C_p$ . However, the existence of resistor R will require extra voltage headroom, which limits the allowable bias current. In the discussions below, different peaking techniques are introduced to improve the bandwidth.

Shown in Fig. 2(a), a series inductor L across R and C is used to create a series peaking in the frequency response. The series inductor creates a second-order RLC resonant circuit with a resonance frequency of  $\omega_0 = 1/\sqrt{LC}$ . In this circuit transfer function is not changed by exchanging R and C since L is in series with in both cases. The transfer function of the series inductive peaking circuit is

$$H_1(S) = \frac{R}{s^2 LC + sRC + 1}$$

$$= \frac{1}{mR^2C^2} \cdot \frac{R}{s^2 + s/mRC + 1/mR^2C^2} \quad . \quad (1)$$

Where  $L = mR^2C$ , m is a dimensionless parameter that defines the poles location and determines the overdamped response of the filter. From (1), the complex conjugate poles are

$$s_{1,2} = -\frac{1}{2mRC} \pm j\sqrt{\frac{1}{mR^2C^2} - \frac{1}{4m^2R^2C^2}}$$

$$= \frac{1}{2mRC\left(-1 \pm j\sqrt{4m-1}\right)}$$

(2)

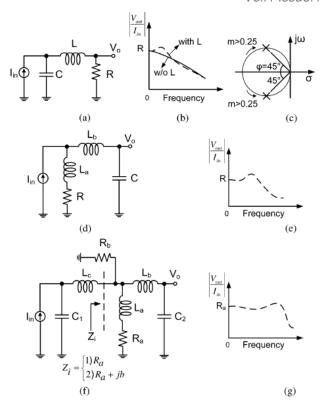

from the frequency response shown in Fig. 2(b), the circuit

including the series peaking inductor improves the bandwidth compare to the circuit without. For this circuit with m = 0.25poles are equal to  $s_1 = s_2 = -2/RC$  near to the critically damped response. As the value of m increases (m > 0.25)poles become complex conjugate and travel along the real axis towards the  $i\omega$  axis, Fig. 2(c). If we equate the standard 2ndorder Butterworth poles with (2), the components values are calculated and maximum gain-flatness response is satisfied. As shown in Fig. 2(c), poles angle  $(\varphi)$  should be equal to 45° from origin to get the maximum gain-flatness response [6]. The circuit in Fig. 2(a) with two reactance components represents one resonance frequency. The circuits with more than two reactance components have more than one resonance mode. A multi-resonance circuit can be utilized to cover a wider range of frequency than a single resonance circuit. For this reason, the resonance frequencies should be chosen properly to optimize the bandwidth of interest.

Now consider the circuit shown in Fig. 2(d). An inductor  $L_a$  in series with R adds a shunt peaking to the series peaking  $L_b$ , results in a shunt-series peaking circuit which improve the bandwidth. The frequency response of this circuit is shown in Fig. 2(e). The transfer function of the shunt-series peaking network is determined as the inductor  $L_a$  in series with R adds a real zero  $-R/L_a$  to the numerator of the transfer function in (3). The inductor  $L_a$  in series with R adds a real zero  $-R/L_a$  to the numerator of the transfer function in (3). The addition of a zero improves the bandwidth but also peaks the response.

Figure .2 (a) Series inductive peaking circuit, (b) frequency response of the circuit (a) with and without L, (c) complex poles location for maximum gainflatness response, (d) shunt-series inductive peaking circuit, (e) frequency response of the shunt-series peaking circuit, (f) series-shunt-series peaking including a T-coil peaking network, (g) series-shunt series peaking frequency response.

$$H_{2}(s) = \frac{V_{0}}{I_{im}} = \frac{sL_{a} + R}{s^{2}C(L_{a} + L_{b}) + sCR + 1}$$

$$= \frac{1}{C(L_{a} + L_{b})} \cdot \frac{L(s + R/L_{a})}{s^{2} + sR/(L_{a} + L_{b}) + 1/C(L_{a} + L_{b})}.$$

(3)

Where from denominator, the complex poles are

$$s_{1,2} = \frac{-R}{2(L_a + L_b)} \pm j \sqrt{\frac{1}{(L_a + L_b)C} - \left(\frac{R}{2(L_a + L_b)}\right)^2}.$$

(4)

The inductor  $L_a$  in series with R adds a real zero  $-R/L_a$  to the numerator of the transfer function in (3). The addition of a zero improves the bandwidth but also peaks the response. To reduce the peaking issue in the frequency response of Fig. 2(e), the components values are equated to the standard 2nd-order

polynomial normalized Butterworth system. For this reason, let us normalize the transfer function  $H_2(s)$  by putting R=1 and C=1 and then

$$L_{a} = m_{1}R^{2}C$$

$$L_{b} = m_{2}R^{2}C, m_{2} < m_{1}$$

(5)

Where  $L_a$  and  $L_b$  are selected to get the maximum gain flatness. Note that in this paper we are trying to keep an agreement between the bandwidth and the gain flatness.

Combining the circuits in Fig. 2(a) and (d), a series-shunt-series circuit which involves a T-coil network  $\left(L_{a-c}\right)$  is resulted in Fig. 2(f). The parasitic capacitors  $C_1$  and  $C_2$  are separated by the T-coil network  $\left(L_{a-c}\right)$ .

In (6), two left hand complex poles extend the bandwidth much further compared to the poles in (3), because the circuit in Fig. 2(f) represents more than one resonance mode. Assuming  $C_2 > C_1$  so poles  $s_{1,2}$  are located at higher frequency than  $s_{3,4}$  poles. Fig. 2(g) illustrates the frequency response improvement of the circuit in Fig. 2(f). If we replace  $R_a$  in (8) and (9) by  $R_a + jb$ , the poles of (7) are obtained. A similar circuit to Fig. 2(f) is presented in [7] which the transfer function of the circuit is normalized to find the relation between the components for maximum bandwidth.

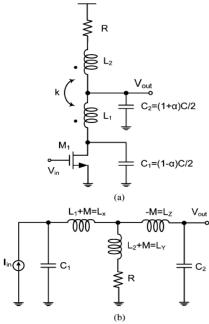

Figure.3. (a) Common-source amplifier with symmetric T-coil peaking network, (b) Simplified small-signal equivalent circuit of the T-coil peaking.

#### III. WIDEBAND AMPLIFIER DESIGN

In this section the series-shunt-series circuit in Fig. 2(f) is applied to a common-source amplifier to realize a wideband LNA design.

## A. Output Peaking Network

The use of 3 inductors in Fig. 2(f) leads to difficulties in the layout. Fortunately, this issue can be resolved through implementation of a center-tap (CT) inductor. The circuit shown in Fig. 3(a) is a common-source amplifier incorporating the CT inductor with a magnetic coupling coefficient k between  $L_1$  and  $L_2$  to form the T-coil peaking network at the output network. The basic functionality of this T-coil network is similar to the circuit in Fig. 2(f) that was explained above.

The CT inductor is employed to save die area and reduce the loss associated with the inductors. The CT inductor with the negative mutual coupling (-M) leads to greater improvements compare to the circuit in Fig. 2(f).

Since only one CT inductor is used in Fig. 3(a), less parasitic components are introduced to the circuit. The equivalent smallsignal model of the output peaking network is shown in Fig. 3(b). Since  $C_2 > C_1$  we assume that  $C_2 = (1+\alpha)C/2$  and  $C_2 = (1-\alpha)C/2$ , where  $0 < \alpha < 1$ . The CT inductor in this network has a symmetrical structure, hence  $L_1 = L_2 = L$ , k = M/L and from here  $L_X = L_Y = L(k+1)$  and  $L_{\rm Z} = -kL$  . The mutual coupling between  $L_{\rm 1}$  and  $L_{\rm 2}$  as an extra term can be exploited to modify the bandwidth extension. In order to optimize the required gain-flatness over the entire bandwidth, k-factor should be determined precisely. For this reason, the relationship between group-delay and the -factor of the T-coil network [Fig. 3(a)] is simulated in Fig. 4. In this simulation the loss of the inductors are included into the circuit model to get more accurate results. As the k-factor increases, flatter group delay over wider bandwidth is resulted. The reason is that the k-factor is limited by the parasitic capacitances and resistances of the inductor. To eliminate the nonideal characteristic of the inductor, stacked top metal layers are implemented while the center-to-center distance of the turnto-turn winding should be reduced [8]. More importantly, if the parasitic capacitances of the output CT inductor become significant, more parasitic capacitances are added to  $C_1$ , which makes  $C_1$  comparable with  $C_2$ . This reduces the desirable bandwidth and makes the bandwidth extension technique inefficient. It is shown in the subsequent section that by increasing  $C_2/C_1$  ratio the bandwidth is further improved.

Figure .4 Group delay response of the T-coil network [4].

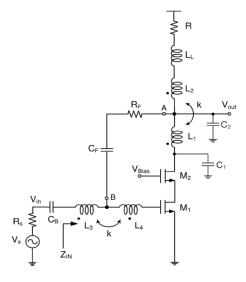

Now, in order to prove the feasibility of the technique explained above, the T-coil peaking network is implemented in a cascode amplifier. Fig. 5 shows the complete single-ended cascode LNA with the CT inductor at the input and the output of this circuit. An extra peaking inductor L<sub>L</sub> is added into the output peaking network as a part of the load, to prevent the gain roll-off and to improve the gain-flatness. A resistor R at the output load in series with L<sub>L</sub> reduces the quality factor of this inductor which extends the bandwidth of the LNA. However, the existence of R causes some drawbacks like peaking in the gain response and additional noise. In order to reduce the peaking in the gain response, a resistive-feedback path is connected across nodes "A" and "B". In Fig. 6 and Fig.7 the frequency response of the wideband LNA with the feedback path is simulated. Clearly, the peaking issues are minimized due to the feedback path effect.

Figure .5 Wideband LNA using symmetrical center-tap inductor (biasing circuitry not shown).

#### IV. EXPERIMENTAL RESULTS

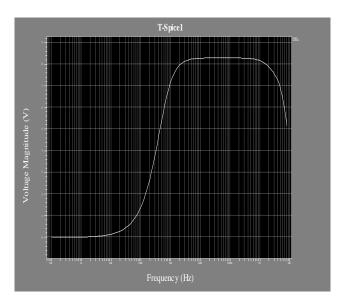

Figure .6 Simulated Frequency Response of Wide Band Low Noise Amplifier.

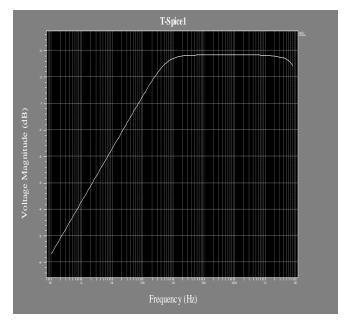

Figure .7 Simulated gain response (dB) of Wide Band Low Noise Amplifier.

#### C. Result Discussion

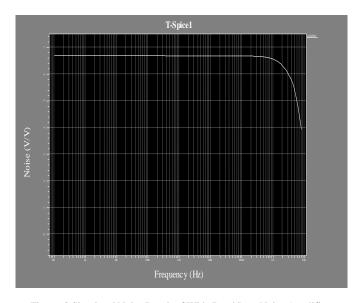

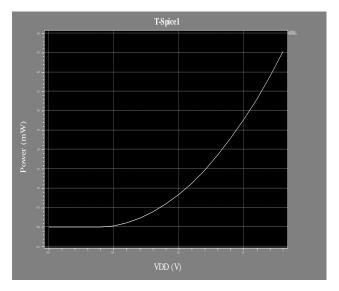

In Fig.6 the simulated frequency response of wide band low noise amplifier is shown. As shown in figure the voltage magnitude over the entire bandwidth is 8.35V. The input AC voltage of low noise amplifier (LNA) is 0.9V so, the gain magnitude of LNA is approximately 9. So, the gain of LNA is approx 19dB. In Fig.7 the simulated gain is shown which is 19 dB. Fig.8 show the simulated noise result of LNA. The noise of wide band LNA is 6 to 8 dB. Fig.9 show the result of total power consuption in wide band LNA which is 4.5mW.

Figure .8 Simulated Noise Result of Wide Band Low Noise Amplifier.

Figure .9 Simulated Static Power Response of Wide Band Low Noise Amplifier.

#### Vol:1 Issue:1 ISSN 2278 - 215X

Table I Performance Comparison of Wide Band LNAs

| References | Technology  | BW(GHz)  | Gain <sub>max</sub> (dB) | NF(dB)  | Power(mW) |

|------------|-------------|----------|--------------------------|---------|-----------|

| [7]        | 0.18μm CMOS | 2.3-9.2  | 9.3                      | 4-8     | 9         |

| [5]        | 0.18μm CMOS | 3.1-10.6 | 9.7                      | 4.5-5.1 | 20        |

| [11]       | 0.18μm CMOS | 0.4-10   | 12.4                     | 4.4-6.5 | 12        |

| This Work  | 0.18μm CMOS | 0.1-8    | 18                       | 6-8     | 4.5       |

#### V. CONCLUSION

In this paper, a technique to attain the wide bandwidth LNA is presented using  $0.18\mu m$  CMOS technology. The intro In this paper, a technique to attain the wide bandwidth LNA is presented using  $0.18\mu m$  CMOS technology. The introduced technique tunes-out the parasitic capacitances of the transistors over a wide bandwidth. The relations of the components to the standard form of the Butterworth filter are calculated to get the desired gain-flatness. The number of inductors is minimized to reduce the loss associated with them. Using this technique, a single stage wideband LNA is obtained with low power consumption.

## **ACKNOWLEDGMENT**

The authors would like to thank Kalol Institute of Technology and Research Centre for their support in this work.

# REFERENCES

- [1] B. Razavi, T. Aytur, C. Lam, F.-R. Yang, K.-Y. Li, R.-H. Yan, H.-C. Kang, C.-C. Hsu, and C.-C. Lee, "A UWB CMOS transceiver," *IEEE J.Solid-State Circuits*, vol. 40, no. 12, pp. 2555–2562, Dec. 2005.

- [2] S. Lou, H. Zheng, and H. C. Luong, "A 1.5-V CMOS receiver front-end for 9-band MB-OFDM UWB system," in *Proc. IEEE Custom Integrated Circuits Conf.*, Sep. 2006, pp. 801–804.

- [3] C. Liao and S. Liu, "A broadband noise-canceling CMOS LNA for 3.1– 10.6-GHz UWB receivers," *IEEE J. Solid-State Circuits*, vol. 42, no. 9, pp. 329–339, Sep. 2007.

- [4] A. Meaamar, C. C. Boon, M. A. Do, and K. S. Yeo, "A 3–8 GHz low noise CMOS amplifier," *IEEE Microw.Wireless Components Lett.*, vol. 19, no. 4, pp. 245–247, Apr. 2009.

- [5] A. Bevilacqua and A. Niknejad, "An ultrawideband CMOS low-noise amplifier for 3.1–10.6-GHz wireless receivers," *IEEE J. Solid-State Circuits*, vol. 39, no. 12, pp. 2259–2268, Dec. 2004.

- [6] D. Feucht, Handbook of Analog Circuit Design. San Diego, CA: Academic, 1990, ch. 8.

- [7] S. Shekhar, J. Walling, and D. Allstot, "Bandwidth extension techniques for CMOS amplifiers," *IEEE J. Solid-State Circuits*, vol. 41, no. 11, pp. 2424– 2439, Nov. 2006.

- [8] J. Long, "Monolithic transformers for silicon RF IC design," IEEE J. Solid-State Circuits, vol. 35, no. 9, pp. 1368–1382, Sep. 2000.