# Voltage Controlled Current Conveyor and its Application

Susheel Sharma<sup>#1</sup> & Rockey Gupta<sup>#2</sup>

<sup>#</sup>Department of Physics and Electronics University of Jammu Jammu-180006, India <sup>1</sup>susheelksharma@gmail.com

<sup>2</sup>rockeygupta@gmail.com

Abstract— In this paper a voltage controlled current conveyor is presented wherein the intrinsic transresistance is controlled by a voltage variable current source which is realized using floatinggate MOSFETs. The resultant conveyor has been used to implement an impedance converter which is further used as inductance simulator. The characteristics of the conveyor and inductance simulation have been obtained through PSpice simulations carried out using level 3 parameters of 0.5  $\mu$ m CMOS technology with supply voltage of ± 0.75 V. The simulation results are found to be in conformity with the mathematical analysis.

Keywords- current controlled current conveyor; current source; inductance simulation

#### I. INTRODUCTION

The second generation current conveyor (CCII) has proved to be a versatile building block being employed in a variety of analog circuits. This device suffers from shortcomings like large voltage tracking error from terminal Y to terminal X due to parasitic resistance at terminal X and the lack of electronic tunability. In 1996, Fabre proposed a BJT based second generation current controlled conveyor (CCCII) by utilizing the parasitic intrinsic transresistance at port X which can be tuned electronically by adjusting the bias current [1-8]. Though BJT has advantage of low noise and high operating frequency, but not compatible with CMOS VLSI technology for integration.

In this paper, we have presented a voltage controlled current conveyor (VCCCII) where the intrinsic resistance of conventional CCCII is controlled by a voltage variable current source realized using floating-gate MOSFETs. The characteristics of the modified current conveyor are studied and it has been further employed for implementing an impedance converter which realizes a tunable inductance simulator.

## II. VOLTAGE CONTROLLED CURRENT CONVEYOR

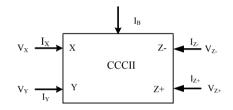

The voltage controlled current conveyor (VCCCII) is a modified form of CCCII which is basically a three port device shown in Fig. 1 and characterized by the following matrix equation.

| $\begin{bmatrix} I_Y \end{bmatrix}$               |   | 0 | 0       | 0 |                                    |

|---------------------------------------------------|---|---|---------|---|------------------------------------|

| $\begin{bmatrix} I_Y \\ V_X \\ I_Z \end{bmatrix}$ | = | 1 | $R_{x}$ | 0 |                                    |

| $\lfloor I_Z \rfloor$                             |   | 0 | ±1      | 0 | $\left\lfloor V_{Z} \right\rfloor$ |

where  $R_x$  is a parasitic resistor present at terminal X and dependents inversely on the bias current(I<sub>B</sub>).

Figure 1. Block diagram of CCCII.

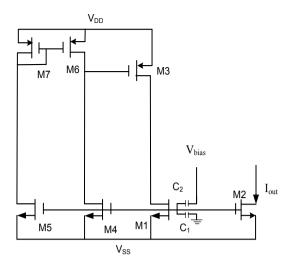

### A. Voltage controlled current source

The bias current in CCCII is generated by a voltage controlled current source (VCCS) as shown in Fig. 2. The circuit of VCCS is based on floating-gate MOSFETs (FGMOS) where the output current is controlled by the bias voltage ( $V_{bias}$ ). Transistors M1 and M2 form the basic FGMOS CM where C<sub>1</sub> is grounded [9-11]. M3 acts as an input current source for M1 which has been suitably biased to feed a variable input current. Transistors M5-M7 form an arrangement to provide a variable bias to M3. It has been achieved by connecting the gate of M3 to the drain of M6 that acts as a constant current is taken from M2 and applied as input bias current to translinear CCCII. The output current of FGMOS based VCCS depends on  $C_2/C_1$  ratio and  $V_{bias}$  and is given as:

$$I_{out} = \frac{\beta_2}{2} \left[ \left( \frac{C_2 / C_1}{1 + C_2 / C_1} \right) V_{bias} - V_T \right]^2$$

(1)

Figure 2. Voltage controlled current source.

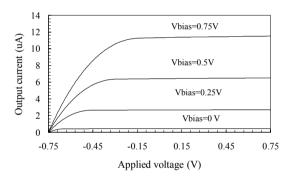

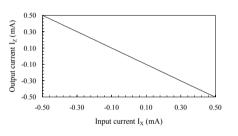

This circuit has been simulated by using level 3 PSpice parameters of 0.5  $\mu$ m technology with supply voltages of  $\pm$  0.75 V by choosing *W/L* ratios for M1 and M2 as 0.5 $\mu$ m/1 $\mu$ m and 100 $\mu$ m/0.5 $\mu$ m for M3, 50 $\mu$ m/1 $\mu$ m for M4 and M5, 50 $\mu$ m/0.5 $\mu$ m for M6 and M7. The variation of output current due to different bias voltages is shown in Fig. 3. The current source has output resistance of 5.56 M $\Omega$  and dissipates 2.31mW power.

Figure 3. Output characteristics of VCCS.

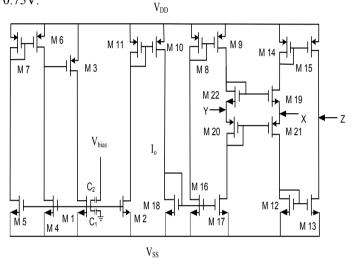

## B. CMOS implementation of VCCCII

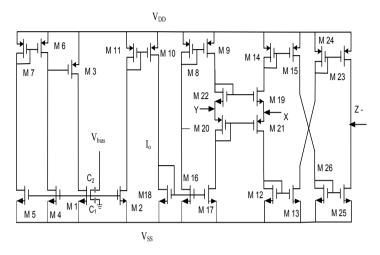

The CMOS implementation of the proposed voltage controlled current conveyor (VCCCII+) is shown in Fig. 4 which has been obtained by using VCCS of Fig. 2 along with the conventional structure of CCCII+ [1, 2]. The VCCS provides different biasing current to CCCII+, therby resulting in different values of intrinsic resistance present at port X.

In Fig. 4 transistors M1-M7 & M10-M11 form a FGMOS based voltage controlled current source which supplies bias current to the translinear loop formed by M19- M22. The rest of the transistors form current mirrors for biasing purpose.

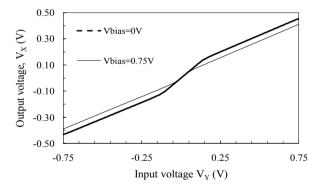

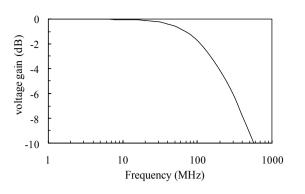

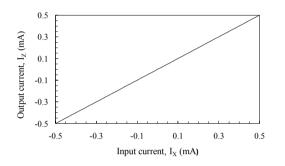

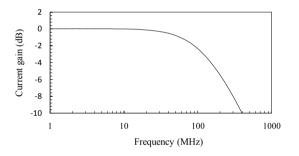

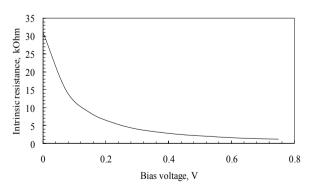

This circuit has been simulated by using level 3 PSpice parameters of 0.5  $\mu$ m technology with supply voltages of  $\pm$ 0.75 V by choosing W/L ratio of 200µm/0.5µm for M16-M18, M12-M13, M22 & M19 and 400um/0.5um for M8-M9, M14-M15. M20 & M21. The transistors M10 and M11 are used to invert the current from voltage controlled current source and have W/L ratios as 50µm/0.5µm. Fig. 5 shows the voltage transfer characteristic of the VCCCII+. The voltage transfer ratio has been found to be 0.998 with a bandwidth 152.27 MHz as shown in Fig. 6. The input resistance at port Y is found to be 3.33 M $\Omega$  and output resistance at port X is 1.2 k $\Omega$ . The current transfer ratio has been found to be unity. The bandwidth for current transfer is found to be 120 MHz as shown in Fig. 8. The input resistance at port X is found to be  $1.22k\Omega$  and output resistance at port Z is 4.49 M $\Omega$ . The variation of intrinsic resistance  $(R_x)$  at port X is shown as a function of bias voltage in Fig. 9. It is found that  $R_r$  varies from  $31k\Omega$  to 1.2 k $\Omega$  as the bias voltage varies from 0V to 0.75V.

Figure 4. Circuit of VCCCII+.

Figure 5. Voltage transfer characteristics of VCCCII.

Figure 6. Frequency response of voltage transfer of VCCCII.

Figure 7. Current transfer characteristics of VCCCII.

Figure 8. Frequency response of current transfer of VCCCII.

Figure 9. Variation of intrinsic resistance with bias voltage.

A negative polarity voltage controlled current conveyor is obtained by inverting the output current of VCCCII+ using a bipolar current mirror as depicted in Fig. 10. The voltage transfer characteristics are found to be similar to that of VCCCII+. The current transfer characteristic is shown in Fig. 11.

Figure 10. Circuit of VCCCII-.

Figure 11. Current transfer characteristics of VCCCII-.

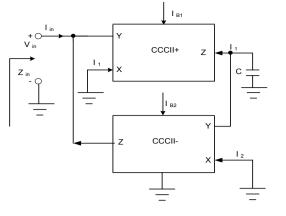

#### III. IMPEDANCE CONVERTER

Impedance converters are often used to simulate inductance using capacitance and to obtain higher values of capacitance from low capacitor value available on chip. Inductance simulation has attracted considerable interest in the implementation of active inductorless filters on the chip, where the use of physical inductors is prohibited due to their size and weight except at high frequencies [12-15]. Impedance converter is realized by connecting a VCCCII+ and VCCCIIas shown in Fig.12. This is equivalent to connecting a positive and a negative transconductor back to back [12, 13].

Figure 12. Circuit of impedance converter.

The analysis of Fig. 12 shows that the input impedance is inductive in nature and is given by:

$$Zin = \frac{V_{in}}{I_{in}} = sRx_1Rx_2C \tag{2}$$

which gives simulated inductance given by:

$$L_{simulated} = R_{x1}R_{x2}C\tag{3}$$

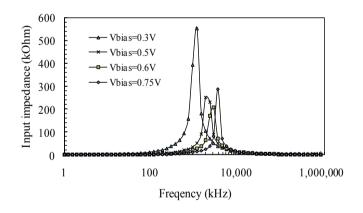

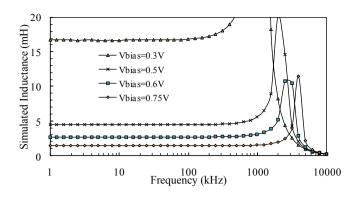

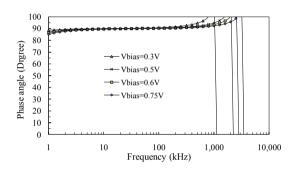

Therefore by terminating the output port of VCCCII+ with a grounded capacitor, we can obtain a grounded inductor. The inductive nature of the input impedance is shown in Fig. 13. The different inductance values are simulated by using different bias voltages with C=1nf as shown in Fig. 14 with respective phase shift in Fig.15. It can be concluded that usable frequency range of simulated inductance decreases with higher value of simulated inductance.

Figure 13. Input impedance of impedance converter.

Figure 14. Voltage variable inductance simulation.

Figure 15. Phase response of different inductance simulations.

The simulation results have been found to be in good agreement with theoretical predictions as shown in following table 1.

| V <sub>bias</sub> | L theoretical | L <sub>simulated</sub> |

|-------------------|---------------|------------------------|

| 0 V               | 961 mH        | 958 mH                 |

| 0.15 V            | 74.24 mH      | 73.5 mH                |

| 0.3 V             | 16.84 mH      | 16.7 mH                |

| 0.5 V             | 4.51 mH       | 4.48 mH                |

| 0.6 V             | 2.73 mH       | 2.71 mH                |

| 0.75 V            | 1.46 mH       | 1.45 mH                |

TABLE I. COMPARISON OF THEORETICAL AND SIMULATED INDUCTANCE

## IV. CONCLUSIONS

In this paper, we have presented the modified form of current controlled current conveyor using a voltage controlled current source. The resultant voltage controlled current conveyor has been characterized and employed in the realization of impedance converter which can simulate a wide range of inductance depending on the value of the bias voltage. The circuit behavior has been studied using PSpice simulations which have been found in good agreement with theoretical results. The tunable inductance can be used to realize inductorless active filters suitable for VLSI integration.

#### REFERENCES

- A. Fabre, O. Saaid and C. Boucherron, "High frequency applications based on a new current controlled conveyor," *IEEE Trans. Circuits Syst.-I:*, 1996, 43 (2), pp. 82-91.

- [2] Costas Psychalinos and George Souliotis, "Low-voltage current controlled current conveyor," *Analog Integr. Circuits Signal Proc.*, 2010, 63, pp. 129–135.

- [3] R. Chaisricharoen, B. Chipipop and B. Sirinaovakul, "CMOS CCCII: structures, characteristics, and considerations," *Int. J. Electron. Commun.*, 2010, 64, pp. 540-557.

- [4] Yan-hui Xi and Li Liu, "A Novel CMOS Current Controlled conveyor II and its Applications", Proc. Intelligent Computation technology and Automation (ICICTA), 2008, pp. 7-10.

- [5] A. Fabre, O. Saaid, F. Wiest and C. Bouchron, "Current controlled bandpass filter based on translinear conveyors," *Electron. Lett.*, 1995, 31(20), pp. 1727-1728.

- [6] H. Barthelemy, and A. Fabre, "A second generation current controlled conveyor with negative intrinsic resistance," *IEEE Trans. Circuits Syst.-I*:, 2002, 49(1), pp. 63–65.

- [7] S. Minaei, D. Kaymak, M. A. Ibrahim and H. Kuntman, "New CMOS configurations for current-controlled conveyors," *Proc. IEEE International Conference on Circuits and Systems for Communications* (ICCSC), 2002, pp. 62-65.

- [8] W. Chunhua, S. Zhixing and L. Haiguang, "New CMOS current controlled second generation current conveyors," *Proc. IEEE International Conference on Circuits and Systems for Communications* (ICCSC), 2008, pp. 333-337.

- [9] S. Yan and E. Sacchez-Sinencio, "Low voltage analog circuit design: A tutorial," *IEICE Trans. Analog Integr. Circuits Syst.*, 2000, E83A (2), pp. 179-196.

- [10] J. Ramirez-Angulo, S. C. Choi and G. G. Altamirano, "Low voltage circuits building blocks using multiple input floating gate transistors," *IEEE Trans. Circuits Syst.-1*, 1995, 42 (11), pp. 971-974.

- [11] Susheel Sharma, S. S. Rajput, L. K. Mangotra and S. S. Jamuar, "FGMOS current mirror: behavior and bandwidth enhancement," *Analog Integr. Circuits Signal Proc.*, 2006, 46, pp. 281-286.

- [12] G. G. A. Black, R. T. Friedmana and A. S. Sedra, "Gyrator implementation with integrable current conveyors," *IEEE J. Solid State Circuits*, 1971, SC-6 (6), pp. 396-399.

- [13] B. Nauta, Analog CMOS filters for very high frequencies, Kluwer Academic Publishers, USA, 1993.

- [14] M. Nishio, H. Sato and T. Suzuki, "A gyrator constructed by CCII with variable current transfer ratio," *Proc. IEEE ISCAS*, 1985, pp. 93-96.

- [15] A. Fabre and O. Saaid, "Novel translinear impedance convertor and bandpass filter application," *Electron. Lett.*, 1993, 29(9), pp. 746-747.